## Letterkenny Institute of Technology

M.Sc. Thesis

Lightweight Cryptography and Authentication Protocols for Secure Communications between Resource-Limited Devices and Wireless Sensor Networks: Evaluation and Implementation

Author: Piotr Książak Student No L00057123

Supervisors:

William Farrelly, M.Sc.

Prof. Paul McKevitt, University of Ulster

**Department of Computing**

Letterkenny, September 2010

## **Declaration**

I hereby declare that for a period of 1 year following the date, on which this dissertation is deposited in the library of the Letterkenny Institute of Technology, the dissertation shall remain confidential with access or copying prohibited. Following the expiry of this period, I permit the librarian of the Institute to allow the dissertation to be copied in whole or in part without reference to me, on the understanding that such authority applies to single copies made for study purposes and is subject to normal conditions of acknowledgement. This restriction does not apply to the publication of the title or abstract of the dissertation.

## **Acknowledgements**

I am pleased to have the opportunity to express my gratitude to all people who helped me accomplish this dissertation.

Firstly, I would like to thank my primary supervisor William Farrelly, Letterkenny Institute of Technology for his day-to-day support, great involvement and a huge amount of patience required to monitor my research. Thank you Billy, without your help this project would not have come to a successful end – it wouldn't even have started.

Secondly, I would like to appreciate the help received from the co-supervisor Prof. Paul McKevitt, University of Ulster and my team-mate Markus Korbel who gave me many useful research hints and had to put up with me on a daily basis. I would also like to thank Mark Leeney for the mathematical-related help as well as Ruth Lennon, Liam McIntyre and the colleagues of the WiSAR project for the help with collecting research sources. I also like to express my gratitude for the help of Dr. David Gray, Cora Tine Teo and Dr. Damien McKeever, Cora Tine Teo who introduced me to the wonderful world of fight-for-a-byte microcontroller programming.

I can't forget to thank people who greatly contributed to the field of the constrained devices security, especially Dr. Pedro Peris Lopez, Delft University of Technology and Dr. François-Xavier Standaert, Université catholique de Louvain who sacrificed his time to clarify some uncertainties. Their work was a backbone to the implementation part of this project.

Finally, I would like to thank my mother Ewa and my fiancée Marta Szymańska who had to put up with my daily complaints about the workload I undertook and helped me to find the time for this.

#### Abstract

This dissertation examines the theoretical context for the security of wireless communication between ubiquitous computing devices and presents an implementation that addresses this need. The number of Resource-Limited Wireless Devices utilized in many areas of the IT industry is growing rapidly. Some of the applications of these devices pose real security threats that can be addressed using authentication and cryptography.

Many of the available authentication and encryption software solutions are predicated on the availability of ample processing power and memory. These demands cannot be met by the majority of ubiquitous computing devices, thus there is a need to apply lightweight cryptography primitives and lightweight authentication protocols that meet these demands in any application of security to devices with limited resources.

The analysis of the lightweight solutions is divided into two major sections: Lightweight Authentication Protocols and Lightweight Encryption Algorithms. Further sections of this work describe the proposed prototype's Wireless Sensor Network including a study of its limitations.

A number of protocols in the field of Authentication and in the field of Encryption are analyzed. The Gossamer Authentication Protocol and the Scalable Encryption Algorithm (SEA) are chosen as the basis of prototype implementation in the Clanguage on a development platform of the 8051-compatible Nordic Semiconductor nRF9E5 microcontroller. A security framework is developed that combines the attributes of the Gossamer protocol and the SEA to provide an implementation of inter-device security. The Gossamer Protocol is additionally used as a means of exchanging session keys for use with the SEA encryption protocol. A brief performance analysis of the prototype running on the nRF9E5 microcontroller is provided by way of conclusion. The resuls of the software implementation of the Gossamer were unsatisfactory both in terms of the code space needs (approximately 1700 bytes excluding shared libraries) and the execution time (almost 150 milliseconds). In contrast, the SEA implementation's results were satisfactory above expectations with the code space requirements smaller than 600 bytes (excluding shared libraries) and the performance of 27 milliseconds per one 96-bit block of data.

## **Table of Contents**

| D  | eclar              | ation  |                                                                                               | . II |  |  |  |  |

|----|--------------------|--------|-----------------------------------------------------------------------------------------------|------|--|--|--|--|

| A  | cknov              | wledg  | gements                                                                                       | Ш    |  |  |  |  |

| Α  | bstra              | ct     |                                                                                               | IV   |  |  |  |  |

| Li | List of FiguresVII |        |                                                                                               |      |  |  |  |  |

| 1. | In                 | trodu  | ction                                                                                         | . 1  |  |  |  |  |

|    | 1.1                | Pro    | ject Background                                                                               | . 1  |  |  |  |  |

|    | 1.2                | Ris    | k Analysis - Pharmaceutical Industry Example                                                  | . 2  |  |  |  |  |

|    | 1.3                | Obj    | ectives                                                                                       | . 3  |  |  |  |  |

|    | 1.4                | Res    | search Hypothesis                                                                             | . 4  |  |  |  |  |

|    | 1.5                | The    | e structure of the Thesis                                                                     | . 4  |  |  |  |  |

| 2. | Se                 | ecurit | y in Wireless Resource-Limited Devices                                                        | . 5  |  |  |  |  |

|    | 2.1                | Ger    | neral Statement of the Problem                                                                | . 5  |  |  |  |  |

|    | 2.2                | Aut    | hentication                                                                                   | . 5  |  |  |  |  |

|    | 2.2.1              |        | Authentication with Resource-Limited Devices                                                  | . 6  |  |  |  |  |

|    | 2.2.2              |        | Known and possible attacks                                                                    | . 7  |  |  |  |  |

|    | 2.2.3<br>Sensor    |        | Identified protocols effective in the context of Infrastructure Wirele Network (IWSN)         |      |  |  |  |  |

|    | 2.3                | End    | cryption                                                                                      | 26   |  |  |  |  |

|    | 2.3                | 3.1    | Problem of Encryption in the context of IWSN                                                  | 26   |  |  |  |  |

|    | 2.3                | 3.2    | Known and possible attacks                                                                    | 27   |  |  |  |  |

|    | 2.3                | 3.3    | Identified algorithms effective in the context of Infrastructure WSN                          | 28   |  |  |  |  |

| 3. | Re                 | esour  | ce-Limited Devices                                                                            | 32   |  |  |  |  |

|    | 3.1                | IWS    | SN introduction.                                                                              | 33   |  |  |  |  |

|    |                    |        | scription of the technical problem of authentication and encryption in t                      |      |  |  |  |  |

|    | 3.3                | Wh     | at are the specific problems associated with Resource Limited Devices                         | 36   |  |  |  |  |

|    | 3.4<br>secu        |        | chnical description of the processor and its implications for effecti                         |      |  |  |  |  |

|    | 3.5<br>secu        |        | chnical description of the memory structure and its limitations for effecting mplementations  |      |  |  |  |  |

|    | 3.6<br>secu        |        | chnical description of the radio transceiver and its limitations for effecting mplementations |      |  |  |  |  |

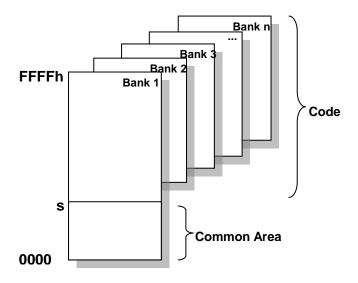

| 3.         | 7          | Ove  | ercoming limitations: Code Banking on the nRF9E5           | 42 |  |  |

|------------|------------|------|------------------------------------------------------------|----|--|--|

| 4.         | Imp        | lem  | entation                                                   | 46 |  |  |

| 4.         | 1          | Har  | dware-related requirements for the implementation          | 46 |  |  |

| 4.         | 2          | Inte | grated Development Environment (IDE) and Hardware utilised | 46 |  |  |

| 4.         | 3          | Des  | sign - algorithms for both authentication and encryption   | 47 |  |  |

| 4.         | 4          | Cod  | ding - Main elements of code explained                     | 50 |  |  |

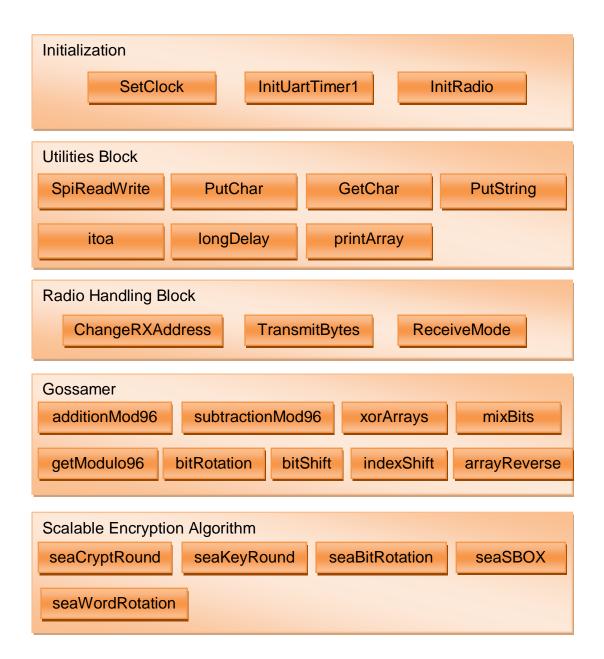

|            | 4.4        | .1   | Gossamer Implementation                                    | 51 |  |  |

|            | 4.4        | .2   | Scalable Encryption Algorithm (SEA) Implementation         | 57 |  |  |

| 4.         | 5          | Tes  | sting                                                      | 62 |  |  |

|            | 4.5        | .1   | Testing environment                                        | 62 |  |  |

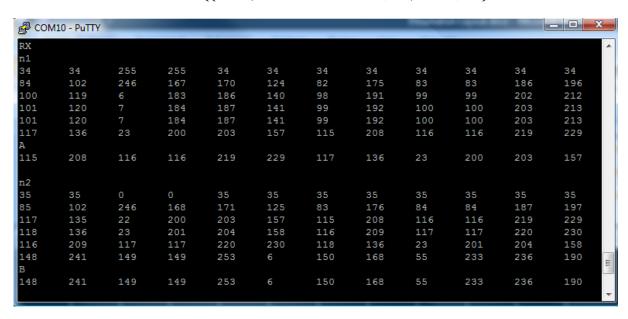

|            | 4.5        | .2   | One Round Step-By-Step Test                                | 62 |  |  |

|            | 4.5        | .3   | Long-term test                                             | 69 |  |  |

| 5.         | Per        | form | nance Analysis                                             | 71 |  |  |

| 5.         | 1          | Mer  | mory Code Space Requirements on nRF9E5                     | 71 |  |  |

| 5.         | 2          | Exe  | ecution Speed                                              | 71 |  |  |

| 6.         | Coı        | nclu | sions and Recommendations                                  | 73 |  |  |

| 6.         | 1          | Cor  | nclusions                                                  | 73 |  |  |

| 6.         | 2          | Red  | commendations for future work                              | 74 |  |  |

| References |            |      |                                                            |    |  |  |

| App        | Appendix A |      |                                                            |    |  |  |

| Δnn        | Annendix B |      |                                                            |    |  |  |

# **List of Figures**

| Figure 1.1  | Risk Analysis Example for the Pharmaceutical Industry          | 2    |

|-------------|----------------------------------------------------------------|------|

| Figure 2.1  | MixBits Function                                               |      |

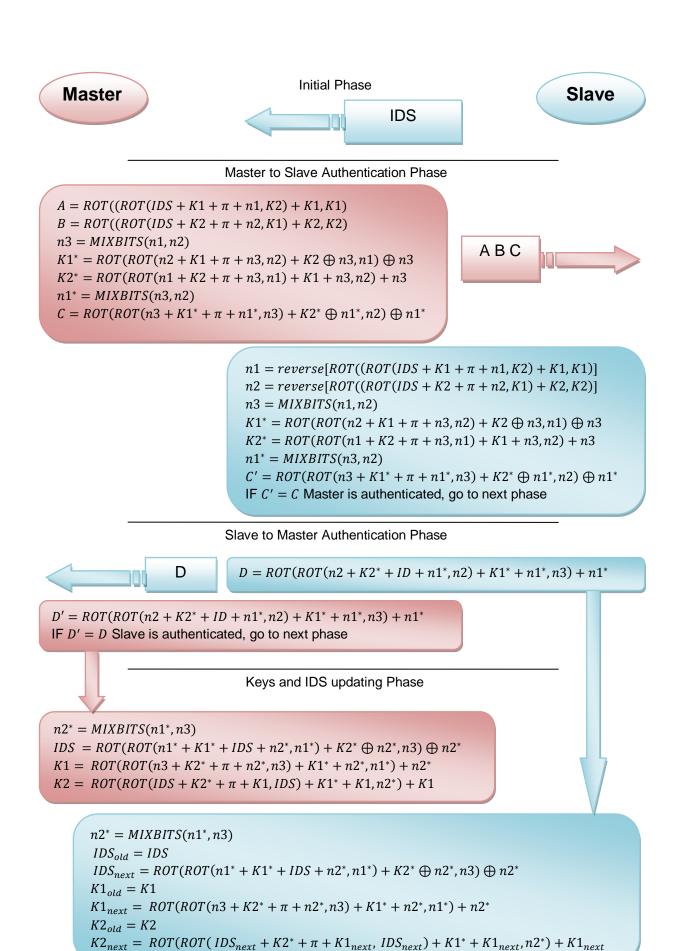

| Figure 2.2  | The Gossamer Protocol                                          | . 18 |

| Figure 2.3  | MixBits function (repeated)                                    | . 19 |

| Figure 2.4  | Modified MixBits Function                                      | . 19 |

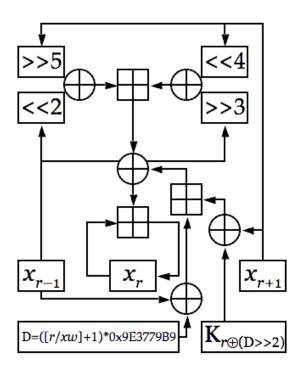

| Figure 2.5  | One round of XXTEA (el Ruptor 2007)                            | . 29 |

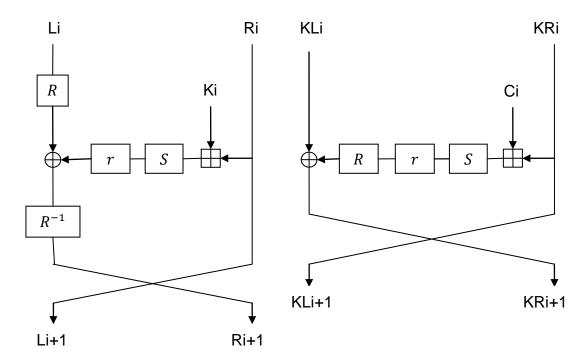

| Figure 2.6  | Encrypt/decrypt and key round of SEA                           | . 31 |

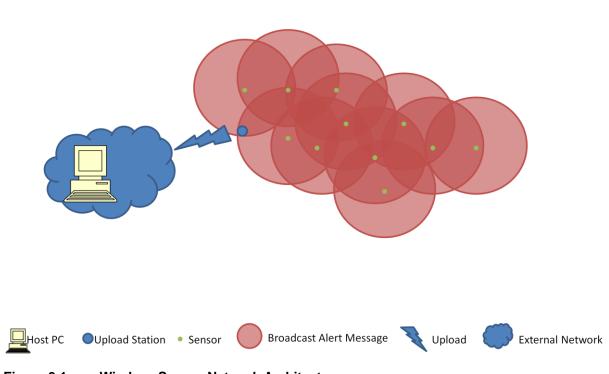

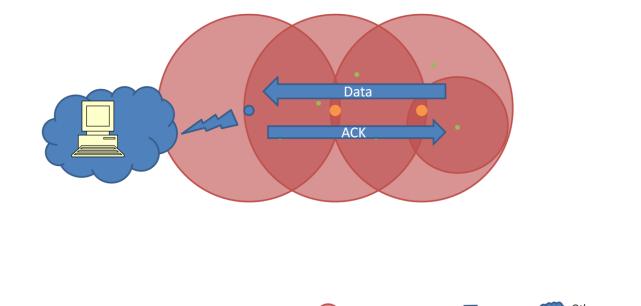

| Figure 3.1  | Wireless Sensor Network Architecture                           | . 33 |

| Figure 3.2  | Infrastructure Wireless Sensor Network Architecture            | . 35 |

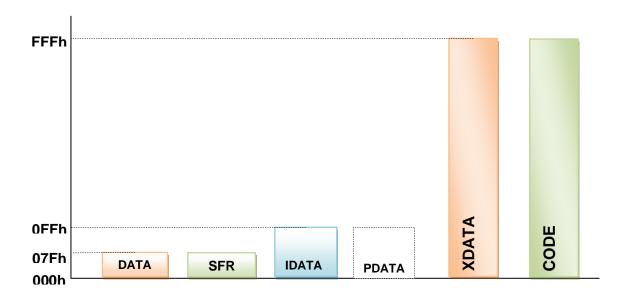

| Figure 3.3  | 8051 Memory Addressing                                         | . 39 |

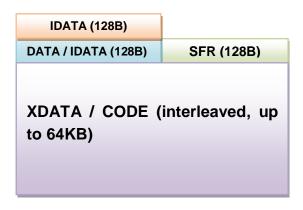

| Figure 3.4  | Physical organization of memory on 8051                        | . 40 |

| Figure 3.5  | NRF9E5 packet structure                                        | . 41 |

| Figure 3.6  | Code Banking Layout                                            | . 43 |

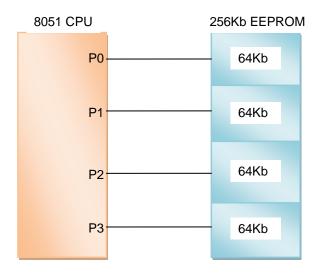

| Figure 3.7  | 8051 with 156Kb EEPROM attached to ports P0-P3                 | . 44 |

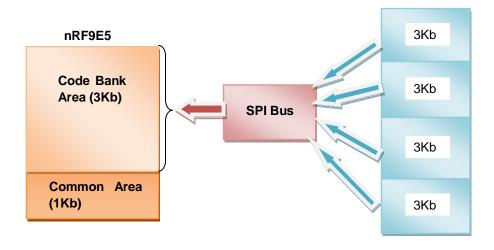

| Figure 3.8  | nRF9E5 code banking with an external SPI-accessed EEPROM       | . 44 |

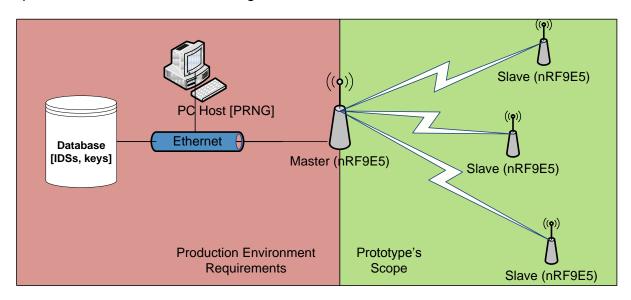

| Figure 4.1  | The Scope of the Implementation part                           | . 47 |

| Figure 4.2  | Gossamer Protocol Adapted to the Infrastructure WSN            | . 49 |

| Figure 4.3  | Main Program Components                                        | . 51 |

| Figure 4.4  | Code: Addition Modulo96                                        | . 52 |

| Figure 4.5  | Code: Subtraction Modulo96                                     | . 53 |

| Figure 4.6  | Code: XOR two 96-bit numbers                                   | . 53 |

| Figure 4.7  | Code: Get Modulo96                                             | . 54 |

| Figure 4.8  | Code: Bit Shift                                                | . 54 |

| Figure 4.9  | Code: Index Shift                                              | . 55 |

| Figure 4.10 | Code: Array Reverse                                            | . 55 |

| Figure 4.11 | Code: Bit Rotation                                             | . 56 |

| Figure 4.12 | MixBits Function pseudocode                                    | . 56 |

| Figure 4.13 | Code: MixBits                                                  | . 57 |

| Figure 4.14 | Code: SEA S-Box                                                | . 57 |

| Figure 4.15 | Code: SEA S-box modified                                       | . 57 |

| Figure 4.16 | Code: SEA Bit-Rotation                                         | . 58 |

| Figure 4.17 | Code: SEA Word-Rotation                                        | . 58 |

| Figure 4.18 | Code: SEA Encrypt/Decrypt Round                                | . 59 |

| Figure 4.19 | Code: SEA Key Round                                            | . 60 |

| Figure 4.20 | Code: SEA Main Function                                        | . 61 |

| Figure 4.21 | Code: Master Side Test Data                                    | . 62 |

| Figure 4.22 | Code: Slave Side Test Data                                     | . 63 |

| Figure 4.23 | Gossamer messages A and B creation (Master)                    | . 63 |

| Figure 4.24 | Gossamer n1 and n2 random numbers extraction (Slave)           | . 64 |

| Figure 4.25 | Gossamer MixBits function, k1next and k2next creation (Master) |      |

| Figure 4.26 | Gossamer MixBits function, k1next and k2next creation (Slave), | . 65 |

| Figure 4.27 | Gossamer message C creation (Master)          | 65 |

|-------------|-----------------------------------------------|----|

| Figure 4.28 | Gossamer message C creation (Slave)           | 66 |

| Figure 4.29 | Gossamer message D creation (Master)          | 66 |

| Figure 4.30 | Gossamer message D creation (Slave)           | 67 |

| Figure 4.31 | Gossamer keys and IDS updating phase (Master) | 67 |

| Figure 4.32 | Gossamer keys and IDS updating phase (Master) | 68 |

| Figure 4.33 | SEA encryption (Master)                       | 68 |

| Figure 4.34 | SEA decryption (Slave)                        | 69 |

| Figure 4.35 | Code: Master Initial Values                   | 70 |

| Figure 4.36 | Code: Slave Initial Values                    | 70 |

## 1. Introduction

The number of Resource-Limited Wireless Devices utilized in many areas of the IT industry is growing rapidly. This growth rate is expected to rise even higher when RFID transponders begin to replace Barcodes on a larger scale. Some of the applications of these devices pose a security threat which can be addressed using cryptographic techniques. Most of the currently used cryptographic solutions are predicated on the existence of ample processing power and memory. These demands cannot be met by the majority of ubiquitous computing devices, thus there is a need to apply lightweight cryptography primitives that meet security demands when considering devices with low resources.

## 1.1 Project Background

This dissertation is written for a fulfilment of the M.Sc. research requirements and a partial fulfilment of the requirements of the Hybrid Inter-Networking Technologies (HINT) Project hosted by the Letterkenny Institute of Technology.

The HINT Project is funded under Enterprise Ireland's Innovation Partnership programme and establishes cooperation between the Letterkenny Institute of Technology and Cora Tine Teo of Falcarragh, Co. Donegal. The main research fields of this project include the integration of various RF technologies (inclusive of Bluetooth, WiFi, and proprietary UHF technologies) and the utilization of Wireless Sensor Networks and active RFID solutions in the context of an item-level stock control and temperature monitoring in the pharmaceutical industry.

One of the key requirements of the HINT project is to provide confidentiality of data exchange between the computing devices used in an entire infrastructure. A major part of this infrastructure will rely on a network of constrained devices with limited memory size and computational power. This M.Sc. will attempt to provide a security framework which can be implemented within the boundaries imposed by Resource-Limited Devices.

## 1.2 Risk Analysis - Pharmaceutical Industry Example

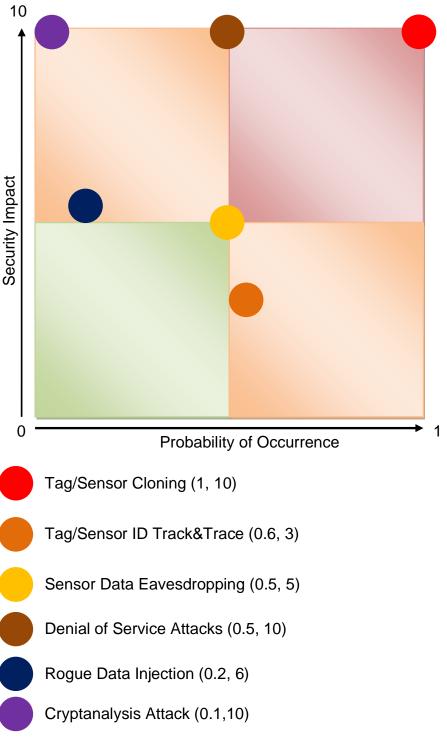

## **Risk Analysis for the Pharmaceutical Industry**

The security impact is measured in the scale of 1 to 10, where 10 is the highest.

Figure 1.1 Risk Analysis Example for the Pharmaceutical Industry

Figure 1.1 illustrates an example of a Risk Analysis concerning the threats associated with the usage of Wireless Sensor Networks or RFID systems for the item-level stock control and temperature monitoring. The following security threats were identified:

- Tag/Sensor cloning a serious threat related to the counterfeiting of medicines with a high likely-hood of occurrence (Juels 2005). Can be addressed with a strong encryption and authentication system. Risk measure = 1\*10 = 10.

- Tag/Sensor tracing a threat related to unauthorised Track & Trace of a Sensor/Tag movement throughout a given area, which has negative privacy implications. It can be addressed with a proper authentication system that doesn't allow the disclosure of a Tag's/Sensor's unique ID. Risk measure = 0.6\*3 = 1.8.

- Data Eavesdropping unauthorized retrieval of sensor/tag data. A strong encryption algorithm provides a counter-measure to this threat. Risk measure = 0.5\*5 = 2.5.

- Denial of Service attack affects the operation of the entire network or a group of Tags/Sensors. The likely-hood of occurrence can be regarded as medium. Such an attack would require appropriate hardware and in-depth knowledge of the radio protocol used. A proper Authentication system provides countermeasures to this threat. Risk measure = 0.5\*10 = 5.

- Rogue-Data Injection an adversary can inject malicious data into the network causing improper configuration of the sensors for example. The probability of occurrence can be low as this kind of attack is not valuable to an adversary in most cases. A Mutual-Authentication system prevents accepting rogue data from unknown sources. Risk measure = 0.2\*6 = 1.2.

- Cryptanalysis Attack secret key discovery through a cryptanalysis attack on the authentication and/or encryption system's secret data. Such an attack compromises the whole security and leads to a full disclosure of all data. The likely-hood of such an event is very low if the encryption key-space is large enough to prevent brute-force attacks (assumes unbreakable algorithm). Risk measure = 0.1\*10 = 1.

#### 1.3 Objectives

The main objectives of this research are as follows:

- To conduct a thorough academic study of authentication and encryption for resource-limited devices.

- To select implementable algorithms for authentication and encryption.

- To select protocols for sensor communications, mutual authentication and establishing secure wireless communication channels.

- To implement a working prototype based on identified algorithms and protocols.

- To evaluate the performance of the prototype.

## 1.4 Research Hypothesis

Lightweight Authentication and Encryption Protocols can be implemented and fulfil basic security requirements of the wireless communication between Resource Limited Devices without hardware modifications.

#### 1.5 The structure of the Thesis

Chapter 2 of this Thesis contains a general statement of the problem and an in-depth study of security solutions for resource-limited wireless communication devices. This chapter is split into two main sections: Authentication and Encryption. Each of these sections provides an introduction to the problem in the context of a prototype Infrastructure Wireless Sensor Network, lists possible attacks and provides an overview of possible solutions.

Chapter 3 introduces the implementation platform (nRF9E5 microcontroller) and the conceptual Infrastructure Wireless Sensor Network used as a reference for the prototype design. This chapter also provides an in-depth study of the limitations of the reference platform in terms of processing power, memory and the radio transceiver capability limitations.

Chapter 4 describes the implementation process and explains the key program functions. The Gossamer Authentication Protocol and the Scalable Encryption Algorithm (SEA) C-language implementations were chosen to create the prototype. At the end of this chapter one can find the results of the prototype testing.

Chapter 5 provides a brief performance analysis of the prototype in terms of code space requirements and the execution speed on the development platform of the 8051-compatible nRF9E5 microcontroller.

Subsequent chapters list conclusions resulting from this research and provide recommendations for future work.

The source code of the software prototype in C-language dedicated for an 8-bit CPU (with minor nRF9E5-specific adaptations) can be found in Appendix B.

## 2. Security in Wireless Resource-Limited Devices

#### 2.1 General Statement of the Problem

Typically, the application of security to wireless networks, such as the Wi-Fi Protected Access specification (Wi-Fi Alliance 2003), requires complex mathematical computation and significant protocol data overhead. Since these requirements cannot be fulfilled by the types of Resource-Limited Devices used in Wireless Sensor Networks (WSN) and Radio Frequency-Identification (RFID) systems due to the constraints imposed by limited computational power, limited memory size and the requirement for low power consumption (Akyildiz et al. 2002), there is a need to provide a lightweight security mechanism that can be implemented within device specifications.

The primary aspects of the security of data exchange are listed by (Menezes et al. 1997):

- Mutual Authentication ensures that all parties involved in communication can trust each other.

- Confidentiality no unauthorised party should be able to view plaintext data.

- Integrity assures that data was not altered during transmission to the recipient.

- Availability ensures that a service is constantly available (the Denial of Service (DoS) attack prevention).

Another important aspect of security especially in the context of Wireless Sensor Networks, is Data Freshness (Perrig et al. 2002) also referred to as Forward Security. Data freshness ensures that the data received is fresh and the adversary cannot replay old messages. Perrig et al. define two types of data freshness: weak, ensuring the order of messages, and strong, allowing additionally for the delay of the message estimation.

This MSc examines the nature of inter-device security in the context Wireless Resource-Limited Devices by decomposition; splitting it into the sub-problems of authentication and encryption. These sub-problems address the key security issues identified in the literature (Schneier 1996, Menezes et al. 1997, Mollin 2007, Ranasinghe & Cole 2008, Karlof et al. 2004).

#### 2.2 Authentication

Mutual Authentication is a process of ensuring that all parties taking part in the communication can validate each other's identity. An intruder should not be able to masquerade as someone else (Schneier 1996). The physical properties of the radio frequency communication channel (the ease of eavesdropping), computational efficiency and power consumption constraints (Akyildiz et al. 2002) impose limitations

on the range of authentication protocols which can be taken under consideration. The problem of authentication in the context of networking resource-limited devices is explained in the following subsections.

#### 2.2.1 Authentication with Resource-Limited Devices

The issue of Authentication in the networking of wireless resource-limited devices was given very little attention until RFID systems became popular. As RFID systems are expected to be widely used for item-level tagging of consumer products the Electronic Privacy Information Center (EPIC) and researchers like Juels (Juels 2006) promoted interest in the issues of privacy and security. One of the first papers to draw attention to these issues was published by Sarma (Sarma et al. 2003). Sarma et al. drew attention to the need for the application of lightweight cryptographic primitives and protocols in the development of solutions for RFID.

The two major threats to consumer's privacy (Juels 2006) are: tracking (traceability) and inventory. Under normal operating conditions, a tag reader will interrogate and read all tags in its proximity. Thus an unsecured RFID tag reveals its unique identifier in the absence of authentication between tag and reader. Any reader compliant with a given RFID specification is able to interrogate and identify the tag. In consequence, a person carrying a given tag, e.g. in a shopping bag, can be tracked around an area by a series of purposely located interrogators without the person's consent. If an unsecured tag conforms to the Electronic Product Code (EPC) specification (Leong et al. 2006) it also carries a unique identification of the item to which it is attached. This poses a threat in respect of itemising the contents of say, a shopping trolley, and identifying an individual's purchasing patterns

Privacy, although drawing most of the attention, is not the only set of issues associated with the absence of an authentication mechanism. RFID systems and Wireless Sensor Networks are facing the threat of data forging and manipulation. Using commonly available equipment an adversary can easily inject messages (Perrig et al. 2002), causing for example false sensor readings.

The majority of commonly used authentication mechanisms rely heavily on computationally intensive mathematical techniques requiring the manipulation of, for example, long keys. Resource Limited Devices share a number of constraints which in the case of RFID systems make the implementation of computationally intensive mathematical routines impossible due mainly to significant reduction in processor power and the absence of sufficient memory to store lengthy keys. A secondary argument is that an increase in the number of logic gates implementated on an Integrated Circuit dramatically increases the overall price per tag (Sarma 2001). Although Wireless Sensor Networks (WSNs) use more capable hardware they are also tightly constrained by power limitations. WSN sensor battery life requirements force limited usage of the CPU and the radio bandwidth. Additionally, a node in a WSN is imbued with many tasks such as the Analogue to Digital Converter (ADC)

readings interpretation, radio protocol handling, reprogramming behaviours etc., thus the code space left for security mechanism implementation is very limited.

In recent years the field of lightweight security has emerged rapidly and is offering solutions mostly for RFID but also covering the area of WSNs. A number of researchers (Juels 2005, Chien 2007, Peris-Lopez et al. 2009, Lee et al. 2009) proposed a group of Ultra-Lightweight Authentication protocols which mainly target RFID but additionally, promise ways of providing a resource-saving authentication mechanism for Infrastructure Wireless Sensor Networks (see Section 3.1) due to their computational simplicity and small data overhead. These protocols are discussed in section 2.2.3 of this document.

#### 2.2.2 Known and possible attacks

Authentication Protocols applicable for a Wireless Network of constrained devices can be grouped into three broad attack categories:

- passive attacks, where the adversary eavesdrops on transmitted messages. In this case we assume that the adversary is not able to alter the messages or inject new ones;

- active attacks, where the adversary is able not only to eavesdrop the communication but also inject new messages or alter and replay the previous ones.

- physical invasive attacks, where the adversary has a physical access and toolset required to access the device's circuitry and for example read the EEPROM memory contents.

While the physical access attack threat cannot be fully negated by a protocol, it has to be noted that the results of such an attack have to be minimised: a compromise of one tag/node should not compromise the security of other nodes/tags. It should not be possible to crack a node's previously recorded and stored communications with a recently discovered key. This requirement is known as the data freshness (see Section 2.1).

#### Traceability (ID disclosure) Attack

It is a requirement of RFID systems and Wireless Sensor Networks that it should not be possible to track nodes without express authority to do so. This is known as a Traceability (ID disclosure) Attack (Juels 2006). The attack is performed to obtain a device's unique ID number which can be further used to track the device's movements using an appropriate RF transceiver. The ID disclosure attack may be performed using passive or active methods and typically targets the authentication protocol as the ID has to be transferred in one of the protocol's messages.

#### **Full Disclosure Attack**

The success of this type of attack means that the entire security of the protocol has been compromised and all secret information used during the protocol flow is disclosed. This allows the adversary to fully impersonate (spoof) one of the devices taking part in the communication and effectively 'Clone' one of the nodes/tags. Typically a full disclosure attack requires active methods, but weak authentication protocols can be fully compromised using passive eavesdropping of consecutive rounds only (Bárász et al. 2007a).

#### **De-Synchronization Attack**

A de-synchronization attack is one of the most serious threats for an authentication protocol that is used in wireless networks. Synchronization means that both parties are aware of the status of the protocol and are able to continue executing the protocol with a normal flow. A de-synchronization attack breaks the protocol by altering the state of one (or both) of the parties authenticating each other in a way which renders further phases of the protocol not executable (Li & Wang 2007). This kind of attack may effectively cause a denial-of-service of one or more nodes in the network.

# 2.2.3 Identified protocols effective in the context of Infrastructure Wireless Sensor Network (IWSN)

This review focuses on Ultralightweight and Lightweight Authentication Protocols and other authentication-related security schemes. Ultralightweight protocols, which were designed for low-cost RFID systems, rely on minimalistic cryptography techniques and provide a viable alternative for securing a heavily constrained Infrastructure Wireless Sensor Network (IWSN) with minor modifications. Other more computationally intensive schemes designed specifically for Wireless Sensor Networks (although filtered by the specific requirements of IWSN) or advanced RFID systems are also discussed.

#### M<sup>2</sup>AP - Minimalist Mutual-Authentication Protocol

Peris-Lopez et al. proposed a family of Ultralightweight Mutual Authentication Protocols (UMAP) initiated by the M²AP (Minimalist Mutual-Authentication Protocol) (Peris-Lopez et al. 2006c). The M²AP proposes a usage of an index-pseudonym (IDS) to avoid disclosing device's ID which prevents the privacy issues (Traceability and Inventory) associated with both RFID and some applications of WSN, for example Wireless Body Sensor Networks (WBSNs). The IDS (96-bit long) is effectively an index to a record in a database storing tag-specific information. Each tag stores a key consisting of four concatenated 96-bit long parts (K = K1 II K2 II K3 II K4). It is assumed that the communication link between a reader and the back-end database is secure.

The protocol is divided into four main stages: tag singulation, mutual authentication, IDS updating and key updating.

- Tag singulation: the reader sends a "hello" message and the tag replies with current IDS. The interrogator can now access a record in the database containing sub-keys K1-K4 associated with a given tag.

- Mutual Authentication is split into two distinct parts: Reader Authentication and Tag Authentication. In the first stage the reader generates two random numbers n1 and n2. The n1 and sub-keys K1 and K2 are used to generate A and B authentication sub-messages which are further concatenated (A II B). The following computation is performed during a round (n) for a tag(i):

$$A \| B \ = IDS_{tag(i)}^{(n)} \oplus K1_{tag(i)}^{(n)} \oplus n1 \parallel (IDS_{tag(i)}^{(n)} \wedge K2_{tag(i)}^{(n)}) \vee n1$$

Where  $\oplus$  = exclusive OR,  $\parallel$  = concatenation,  $\wedge$  = logical AND,  $\vee$  = logical OR.

The n2 number and K3 key are used to generate sub-message C (further used to update the IDS and the key K):

$$C = IDS_{tag(i)}^{(n)} + K3_{tag(i)}^{(n)} + n2$$

These sub-messages are then concatenated and sent to the tag (message = A II B II C).

The next stage is the Tag Authentication. The Tag uses sub-messages A and B to authenticate the reader. The message C provides random number n2 which is used by the Tag to update the key K and the IDS. After a successful reader authentication the tag sends a message comprising of two concatenated sub-messages D II E.

$$D = (IDS_{tag(i)}^{(n)} \vee K4_{tag(i)}^{(n)}) \wedge n2$$

$$E = (IDS_{tag(i)}^{(n)} + ID_{tag(i)}) \oplus n1$$

Sub-message D allows the reader to authenticate the tag. Part E is used to send the ID in a secure form.

IDS Updating: in case of a successful authentication the reader and the tag update the index-pseudonym using the following operation:

$$IDS_{tag(i)}^{(n+1)} = (IDS_{tag(i)}^{(n)} + (n2 \oplus n1)) \oplus ID_{tag(i)}$$

Key Updating: after a completion of the IDS updating the reader and the tag have to update all 4 sub-keys K1-K4 using the following equations:

$$K1_{tag(i)}^{(n+1)} = K1_{tag(i)}^{(n)} \oplus n2 \oplus (K3_{tag(i)}^{(n)} + ID_{tag(i)})$$

$$\begin{split} K2_{tag(i)}^{(n+1)} &= K2_{tag(i)}^{(n)} \oplus n2 \oplus (K4_{tag(i)}^{(n)} + ID_{tag(i)}) \\ K3_{tag(i)}^{(n+1)} &= (K3_{tag(i)}^{(n)} \oplus n1) + (K1_{tag(i)}^{(n)} + ID_{tag(i)}) \\ K4_{tag(i)}^{(n+1)} &= (K4_{tag(i)}^{(n)} \oplus n1) + (K2_{tag(i)}^{(n)} + ID_{tag(i)}) \end{split}$$

Peris-Lopez et al. chose only simple operations ( $\bigoplus$ ,  $\land$ ,  $\lor$  and sum mod  $2^{96}$ ) forced by the computational power constraints of low-cost RFID tags and tag reading speed requirements (limited time for computation). He claims that the probability of ones and zeros in every sub-key is spread almost evenly and the Hamming distance between two consecutive keys  $K1_{tag(i)}^{(n)}$  and  $K1_{tag(i)}^{(n+1)}$  is 47.5 bits on average.

The protocol's author provided a security analysis of the proposal in terms of resistance to ID disclosure, Man-in-the-middle, replay attacks and Data Integrity assurance. The anonymity of the tag (ID hiding) is ensured by the usage of an index-pseudonym (IDS). The Data Integrity is guaranteed by the IDS and four sub-keys the attacker would have to be able to modify these values on both the database and the tag, otherwise even a single bit manipulation would stop the protocol execution. The mutual authentication mechanism based on two random numbers refreshed with every iteration of the protocol renders the Man-in-the-middle attack impossible. Peris-Lopez et al. also claimed that the IDS and sub-keys updating mechanism prevents Replay Attacks.

The M<sup>2</sup>AP was analysed and proven insecure by (Bárász et al. 2007b). Bárász describes specifications of a passive attack (eavesdropping only) against the M<sup>2</sup>AP which is able to retrieve the IDS and all sub-keys by eavesdropping over a few consecutive runs of the protocol. Two main weaknesses of the M2AP were discovered. The first is the fact that the usage of the bit-wise operations and the modulo 296 addition only implies that every bit affects only bits which are to the left of it and the least significant bit is independent of any other bits. Such operations are called triangular functions or T-functions and per Klimov and Shamir "A T-function is a mapping in which the i-th bit of the output can depend only on bits 0,1,..., i of the input"(Klimov & Shamir 2004). The second weak part is the OR and AND operations used in messages B and D which can help to derive n1 and n2 values with the help of set and reset bits of IDS. Bárász showed that the attacker can learn the ID, K1, K3, n1 and n2 after eavesdropping only two consecutive rounds of the M<sup>2</sup>AP which already allows for Traceability of the tag. K2 and K4 sub-key discovery requires eavesdropping more rounds but provides the attacker with the ability to impersonate the Tag or the Reader.

#### **EMAP - An Efficient Mutual-Authentication Protocol**

After weaknesses (Bárász et al. 2007b) were discovered in the M²AP Protocol, Peris-Lopez et al. proposed a new EMAP Protocol (Peris-Lopez et al. 2006a). The protocol is similar in concept to the M²AP: It has the same four stages and uses IDS and four sub-keys K1-K4. The only changes which were applied were the mathematical operations used to construct sub-messages A, B, C, D, E and the formulas for updating the IDS and four sub-keys. The new formulas for the sub-messages are as follows:

$$A = IDS_{tag(i)}^{(n)} \oplus K1_{tag(i)}^{(n)} \oplus n1$$

$$B = (IDS_{tag(i)}^{(n)} \vee K2_{tag(i)}^{(n)}) \oplus n1$$

$$C = IDS_{tag(i)}^{(n)} \oplus K3_{tag(i)}^{(n)} \oplus n2$$

$$D = (IDS_{tag(i)}^{(n)} \wedge K4_{tag(i)}^{(n)}) \oplus n2$$

$$E = (IDS_{tag(i)}^{(n)} \wedge n1 \vee n2) \oplus ID_{tag(i)} \oplus K1_{tag(i)}^{(n)} \oplus K2_{tag(i)}^{(n)} \oplus K3_{tag(i)}^{(n)} \oplus K4_{tag(i)}^{(n)}$$

The IDS updating formula was supposed to have better statistical properties than the M<sup>2</sup>AP as the entire number use bit-wise XORed with a random number n<sup>2</sup>.

$$IDS_{tag(i)}^{(n+1)} = IDS_{tag(i)}^{(n)} \oplus n2 \oplus K1_{tag(i)}^{(n)}$$

The key updating formulas now contain a parity function  $(F_{p(X)})$  which divides the 96-bit number into 24 4-bit blocks, calculates and outputs a parity bit for each block. The formulas are as follows:

$$K1_{tag(i)}^{(n+1)} = K1_{tag(i)}^{(n)} \oplus n2 \oplus (ID_{tag(i)}(1:48) \left\| F_p(K4_{tag(i)}^{(n)}) \right\| F_p(K3_{tag(i)}^{(n)}))$$

$$K2_{tag(i)}^{(n+1)} = K2_{tag(i)}^{(n)} \oplus n2 \oplus (F_p(K1_{tag(i)}^{(n)}) \left\| F_p(K4_{tag(i)}^{(n)}) \right\| ID_{tag(i)}(49:96))$$

$$K3_{tag(i)}^{(n+1)} = K3_{tag(i)}^{(n)} \oplus n1 \oplus (ID_{tag(i)}(1:48) \left\| F_p(K4_{tag(i)}^{(n)}) \right\| F_p(K2_{tag(i)}^{(n)}))$$

$$K4_{tag(i)}^{(n+1)} = K4_{tag(i)}^{(n)} \oplus n1 \oplus (F_p(K3_{tag(i)}^{(n)}) \left\| F_p(K1_{tag(i)}^{(n)}) \right\| ID_{tag(i)}(49:96))$$

The security analysis provided by Peris-Lopez et al. was largely similar to the one provided in M<sup>2</sup>AP specification.

(Li & Deng 2007) highlighted the weaknesses of the protocol allowing for a desynchronization and a full disclosure attack. It was highlighted that the tag is not able to verify if the reader successfully received correct messages D and E and updated the keys and IDS accordingly. Li & Deng described two types of possible attacks on LMAP: de-synchronization attack and full disclosure attack. As both of the protocols rely on a synchronization of IDS and keys stored on a tag and in the back-end database, a full round of the protocol has to take place in order to keep synchronization on both sides. Li & Deng proposed two man-in-the-middle desynchronization attacks:

- Changing the message C by intercepting message (A II B II C) and XORing sub-message C with a series of zeros excluding the least significant bit set to 1 and forwarding the set of messages to the tag. The tag can still authenticate the reader as A and B remain unchanged, but it will get the wrong n2 number. Despite this the protocol will continue and the tag will reply with incorrect D and E messages; however, the reader will not be able to discover changes in D and will accept in all cases. It was shown that there is a 75% chance on average that the reader will accept an incorrect value E and update its database using original n2. The tag will do the same using incorrect n2 and both devices will lose synchronization.

- Changing the messages A and B similar to the previous attack but in this case A and B sub-messages are altered and in the result n1 value used by the tag for an update is changed.

The full disclosure attack is based on a stateless nature of the tags - there is no way to save the state of the protocol execution on a tag. The attack consists of four stages, the first three of which are performed on a single protocol run and disclose all secret values apart from K2, K4 and the tag ID. The fourth stage requires approximately  $(\log_2 m - 1)$  runs to fully disclose tag's ID (m-bits long).

#### LMAP - A Real Lightweight Mutual Authentication Protocol

After several weaknesses were discovered in M²AP and EMAP Peris-Lopez et al addressed them in the LMAP proposal (Peris-Lopez et al. 2006b). LMAP and EMAP share some similarities: the same size of the IDS and the same size and number of sub-keys. However, the Tag to Reader message (previously consisting of sub-messages D and E) was reduced only to a single message D. The rest of the sub-messages are now created using the following equations:

$$A = IDS_{tag(i)}^{(n)} \oplus K1_{tag(i)}^{(n)} \oplus n1$$

$$B = (IDS_{tag(i)}^{(n)} \vee K2_{tag(i)}^{(n)}) + n1$$

$$C = IDS_{tag(i)}^{(n)} + K3_{tag(i)}^{(n)} + n2$$

$$D = (IDS_{tag(i)}^{(n)} + ID_{tag(i)}) \oplus n1 \oplus n2$$

The IDS index-pseudonym is now created with the following operation:

$$IDS_{tag(i)}^{(n+1)} = (IDS_{tag(i)}^{(n)} + (n2 \bigoplus K4_{tag(i)}^{(n)})) \bigoplus ID_{tag(i)}$$

The sub-key K1 and K2 equations are identical to the ones proposed in M<sup>2</sup>AP:

$$K1_{tag(i)}^{(n+1)} = K1_{tag(i)}^{(n)} \oplus n2 \oplus (K3_{tag(i)}^{(n)} + ID_{tag(i)})$$

$$K2_{tag(i)}^{(n+1)} = K2_{tag(i)}^{(n)} \oplus n2 \oplus (K4_{tag(i)}^{(n)} + ID_{tag(i)})$$

The operations used to create the last two sub-keys K3 and K4 were slightly modified in comparison to M<sup>2</sup>AP and are as follows:

$$K3_{tag(i)}^{(n+1)} = (K3_{tag(i)}^{(n)} \oplus n1) + (K1_{tag(i)}^{(n)} \oplus ID_{tag(i)})$$

$$K4_{tag(i)}^{(n+1)} = (K4_{tag(i)}^{(n)} \oplus n1) + (K2_{tag(i)}^{(n)} \oplus ID_{tag(i)})$$

The LMAP and the M<sup>2</sup>AP protocols were analysed by (Li & Wang 2007) and serious weaknesses were discovered in both. The vulnerabilities highlighted and possible attacks are very similar to the EMAP security flaws analysis in (Li & Deng 2007). Again, the main issue is related to the fact that the tag is not able to verify if the reader successfully received and verified message D, which may lead to a protocol de-synchronization. The de-synchronization attacks are practically identical to the one proposed earlier: message C alteration and messages A&B alteration attacks performed by XOring the message with zeros and one as the least significant bit. The probability of the success of the first attack remained at 50%. The full disclosure attack is slightly more difficult than in the case of the M<sup>2</sup>AP protocol. The attacker has to obtain the current IDS of the tag and then try all possible (A II B II C) messages by sending them to the tag and changing the j-th bit in A and B at each try. This reveals the n1 random number value and allows the calculation of K1 and K2. The rest of the secret values can be discovered by interacting with the reader and the tag one more time and then derived from the known sub-message creation equations and a simple algorithm described in (Li & Wang 2007). Several countermeasures were proposed, the most interesting one proposes a tag status storage mechanism preventing desynchronization attacks: an additional status bit on the tag indicating whether a protocol has been successfully completed and two additional 96-bit memory spaces for storing n1 and n2 values used in the last protocol run. A Similar mechanism was included in (Peris-Lopez et al. 2006b) as a LMAP+ extension.

However, the above protocols including Li & Wang's countermeasures were proven still susceptible to de-synchronization and full disclosure attacks by (Chien & Huang 2007). Chien & Huang showed that the attacker can flip some bits without being noticed by the reader or the tag so the protocol round would complete and both sides would update the IDS and keys with different n1 and n2 random numbers. The authors also revised the Li & Wang's full disclosure attack and showed even more efficient version of the attack.

The Li & Wang's paper was also followed by (Bárász et al. 2007a) describing a fully passive full disclosure attack against LMAP, which requires only eavesdropping a few (about 10) consecutive rounds of the protocol. The main weaknesses of the protocol mentioned in (Bárász et al. 2007b) were related to triangular functions properties (weak propagation of bits from left to right).

### SASI - Strong Authentication and Strong Integrity

The family of UMAP protocols proposed by Peris-Lopez et al. influenced an interesting SASI protocol specification by (Chien 2007). The concept is similar to that of the UMAP family. The tag has a unique 96-bit ID and pre-shares an index-pseudonym (IDS) and two keys K1 and K2 with a back-end database accessible by the reader (secure link assumed). In order to resist de-synchronization a state-verification has been employed: the tag stores two sets of (IDS, K1, K2) – the old values and the potential new values. In each protocol instance the reader may probe the tag twice: the first time the tag replies with its potential new IDS and if it was not found it may probe the tag again and this time the tag will use the old IDS value.

The protocol flow is also similar to UMAP family:

- The reader sends a "hello" message.

- The tag replies with its potential next IDS.

- The reader uses IDS to find a matched record in the database. It generates two random values n1 and n2 and uses stored keys K1 and K2 to generate messages A, B and C which are further concatenated and sent to the tag. The following equations are used to generate A and B:

$$A = IDS_{tag(i)}^{(n)} \oplus K1_{tag(i)}^{(n)} \oplus n1$$

$$B = (IDS_{tag(i)}^{(n)} \vee K2_{tag(i)}^{(n)}) + n2$$

Keys K1 and K2 are rotated using a rotation function 'ROT', which was not clearly specified in Chen's paper but revealed in (Hernandez-Castro et al. 2008) to be a Hamming rotation. The rotations are described as follows:

$$\overline{K}1 = ROT(K1 \oplus n2, K1)$$

$$\overline{K}2 = ROT(K2 \oplus n1, K2)$$

According to Hernandez-Castro et al. Chien intended to use a Hamming rotation  $ROT(A,B) = A \ll wt(B)$ , where wt(B) stands for the Hamming weight of vector B. If a modular rotation  $ROT(A,B) = A \ll BmodN$  was chosen, then the protocol would be susceptible to a passive attack proposed in (Hernandez-Castro et al. 2008).

After rotations are performed, the rotated and original keys are used to form the message C:

$$C = (K1 \oplus \overline{K}2) + (\overline{K}1 \oplus K2)$$

The tag receives A II B II C and extracts n1 from A, and n2 from B. Then it

performs the same two rotation functions as the reader in previous step,

calculates message C and compares it with the received one. Upon successful

verification the tag replies to the reader with a message D:

$$D = (\overline{K}2 + ID) \oplus ((K1 \oplus K2) \vee \overline{K}1)$$

After sending the message the tag updates the IDS and keys K1 and K2 using the following equations:

$$IDS_{old} = IDS; \ IDS_{next} = ((IDS + ID) \oplus (n2 \oplus \overline{K}1))$$

$K1_{old} = K1; \ K1_{next} = \overline{K}1$   $K2_{old} = K2; \ K2_{next} = \overline{K}2$

• After the message was received and successfully verified by the reader, the reader updates the IDS and keys entries using the same equations as the tag.

Chien provided a security analysis of the protocol claiming that it is secure against de-synchronization attacks, ID disclosure attacks and it should provide privacy, anonymity, mutual authentication and forward secrecy (keeping the past communication secure even if a tag is compromised later) while retaining the ultralightweight properties and requiring a message length of 4L<sup>1</sup> and the total memory size on a tag of 7L as opposed to 6L in UMAP family protocols.

There have been no published successful passive attacks against the SASI protocol using Hamming rotation function. However, several active attack possibilities were discovered. Two de-synchronization attacks on the SASI protocol were described by (Sun et al. 2008). Both attacks were targeting the anti-de-synchronization mechanism of the SASI protocol: the possibility of re-trying the communication with the old IDS in case the next-possible IDS was not found in the database. Another paper by (Cao et al. 2009) described a denial-of-service and ID disclosure attacks. A desynchronization, ID disclosure and finally a full disclosure attack against the SASI protocol was proposed by (D'Arco & De Santis 2008).

#### **Gossamer Protocol**

The Gossamer Protocol derived by (Peris-Lopez et al. 2009) is one of the most recent proposals in the field of lightweight cryptography. Peris-Lopez et al. summarized that most of the weaknesses are related to the fact that all simple bitwise operations like AND, OR, XOR and modulo  $2^{96}$  addition are T-functions (Klimov & Shamir 2004), thus suffer from weak propagation of bits from left to right. Another weakness highlighted was the bias in the probability (75%) of obtaining a bit '1' when using bitwise AND operation.

Peris-Lopez proposes a Gossamer Protocol that is largely similar to the SASI protocol in general concept: each tag has a static identifier (ID), an index-pseudonym (IDS) and two keys K1 and K2 in memory. Additionally each tag is required to store two sets of the tuple (IDS, K1, K2): old value and the potential next value. It is assumed that the only mathematical operations that will be used are bitwise XOR,

<sup>&</sup>lt;sup>1</sup> L denotes the length of one key or the IDS in bits. 96-bits in the case of the EPC RFID specifications.

addition modulo  $2^m$  and left rotation function Rot(x,y). The rotation function performs a circular shift on the value of x by  $(y \ mod \ N)$ , positions to the left for a given N (96 in case of the EPC RFID). The most computationally expensive operation of generating two random numbers required in each protocol run is designed to be done on the reader side. An additional security layer is added with a lightweight function called MixBits, which is based on a methodology described in (Hernandez-Castro et al. 2006) and uses only bitwise right shift. The pseudocode describing the algorithm for the MixBits function is shown in Figure 2.1.

$$Z = MixBits (X, Y)$$

$Z = X$

FOR counter = 0 to 32

$Z = (Z >> 1) + Z + Z + Y$

ENDFOR

Figure 2.1 MixBits Function

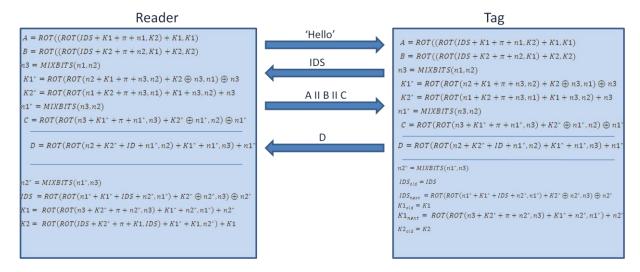

The author of the protocol divided it into three stages: tag identification, mutual identification and updating phase.

- Tag Identification phase just as in previously described SASI protocols the reader sends a "hello" message and the tag replies with its next potential IDS<sub>next</sub>. The reader performs a search in the database to find a matching entry and if successful it continues to the next phase. Otherwise the reader queries the tag again and the tag replies with the old IDS<sub>old</sub>.

- Mutual Authentication phase the reader generates two random values n1 and n2 and build messages A, B and C using the following equations (assuming that  $\pi = 0x3243F6A8885A308D313198A2 96$  bits):

$$A = ROT((ROT(IDS + K1 + \pi + n1, K2) + K1, K1)$$

$$B = ROT((ROT(IDS + K2 + \pi + n2, K1) + K2, K2)$$

$$n3 = MIXBITS(n1, n2)$$

$$K1^* = ROT(ROT(n2 + K1 + \pi + n3, n2) + K2 \oplus n3, n1) \oplus n3$$

$$K2^* = ROT(ROT(n1 + K2 + \pi + n3, n1) + K1 + n3, n2) + n3$$

$$n1^* = MIXBITS(n3, n2)$$

$$C = ROT(ROT(n3 + K1^* + \pi + n1^*, n3) + K2^* \oplus n1^*, n2) \oplus n1^*$$

Now the tag extracts n1 from A and n2 from B and performs the same operations as the reader to construct  $\mathcal{C}^*$ . Then it compares  $\mathcal{C}$  received with  $\mathcal{C}^*$  calculated and upon success constructs message D to be sent to the reader:

$$D = ROT(ROT(n2 + K2^* + ID + n1^*, n2) + K1^* + n1^*, n3) + n1^*$$

The tag performs Tag Updating phase. The reader upon receiving message D performs the same calculation and compares D received with  $D^*$  calculated. If this is successful the reader performs Updating phase.

• Updating phase – the tag updates the two (IDS, K1, K2) tuples as follows:

$$n2^* = MIXBITS(n1^*, n3)$$

$$IDS_{old} = IDS$$

$$IDS_{next} = ROT(ROT(n1^* + K1^* + IDS + n2^*, n1^*) + K2^* \oplus n2^*, n3) \oplus n2^*$$

$$K1_{old} = K1$$

$$K1_{next} = ROT(ROT(n3 + K2^* + \pi + n2^*, n3) + K1^* + n2^*, n1^*) + n2^*$$

$$K2_{old} = K2$$

$$K2_{next} = ROT(ROT(IDS_{next} + K2^* + \pi + K1_{next}, IDS_{next}) + K1^* + K1_{next}, n2^*)$$

$$+ K1_{next}$$

The reader updates the back-end database using the following formulas:

$$n2^* = MIXBITS(n1^*, n3)$$

$$IDS = ROT(ROT(n1^* + K1^* + IDS + n2^*, n1^*) + K2^* \oplus n2^*, n3) \oplus n2^*$$

$$K1 = ROT(ROT(n3 + K2^* + \pi + n2^*, n3) + K1^* + n2^*, n1^*) + n2^*$$

$$K2 = ROT(ROT(IDS + K2^* + \pi + K1, IDS) + K1^* + K1, n2^*) + K1$$

The protocol requires exchanging four messages between the reader and the tag. All stages are illustrated in Figure 2.2. Hello message length is not specified, the IDS and D messages are 96-bits long and the concatenated A II B II C message consist of three 96-bit long sub-messages. A total of 384 bits (excluding Hello message) needs to be transmitted during one protocol run.

The Storage Requirements on the tag side are limited to 7 times the key-length (96-bits in the original specification) to hold two IDS, K1, K2 tuples and the static identifier ID. Each database record is required to story only one IDS, K1, K2 tuple and the static ID.

Figure 2.2 The Gossamer Protocol

The Gossamer Protocol prevents attacks listed in section 2.2.2 as follows:

- ID Disclosure Attack the notion of an index-pseudonym (IDS) and private keys K1 and K2 changed for every authentication session prevents disclosure of the unique identifier (ID) of the tag.

- Full Disclosure Attack the secret data (ID, K1, K2) is always scrambled using two random numbers and sum, Mixbits and Rot functions before being transmitted over the wireless link.

- De-Synchronization Attack each tag stores (IDS, K1, K2) tuples used in a previous protocol run. In case of an unsuccessful update on the reader side in the last stage of the protocol (message D) the tag can be still identified using old values. The result is that both the tag and the reader can recover their synchronized state.

The requirement of the Data Freshness (see section 2.1) is fulfilled by updating secret values K1, K2, n1 and n2 at each protocol run.

To the knowledge of the author only one paper describing attacks against the Gossamer protocol was published (Ahmed et al. 2010) shortly before this dissertation was finished. Ahmed et al. described two attacks against the protocol. The first one was feasible if both random numbers n1 and n2 were equal to zero allowing the discovery of all secret values after eavesdropping two consecutive runs of the protocol. The latter attack concerned a case where both K1 and K2 values are equal to zero which leads to disclosure of all secret values during a single authentication round. Ahmed et al. proposed modifications to the protocol. However their proposal has a major flaw in that it renders the extraction of n1 and n2 impossible.

The original Gossamer protocol is given in fig. 2.1 replicated below for clarity of explanation.

$$A = ROT((ROT(IDS + K1 + \pi + n1, K2) + K1, K1))$$

$$B = ROT((ROT(IDS + K2 + \pi + n2, K1) + K2, K2))$$

An attack on the original Gossamer protocol is feasible if both random numbers n1 and n2 were equal to zero permitting the discovery of K1 and K2 after eavesdropping two consecutive runs of the protocol.

The proposed Ahmed et al modification substitutes K1 for n2 in A and K2 for n1 in B.

$$A = ROT((ROT(IDS + K1 + \pi + n1, K2) + K1, \mathbf{n2})$$

$$B = ROT((ROT(IDS + K2 + \pi + n2, K1) + K2, \mathbf{n1})$$

The values n1 and n2 are known to the reader. In A above,  $ROT(IDS + K1 + \pi + n1, K2) + K1$  is rotated by n2 by the reader and likewise in B,  $ROT(IDS + K2 + \pi + n2, K1) + K2$  is rotated by n1. Messages A & B are exchanged with the tag. The tag's job is to extract the values n2 and n1 from messages A and B and to perform the appropriate inverse rotation to verify the remainder of the contents of messages A and B. However, in this modification, the tag is not aware of the value n1 or n2 and therefore cannot perform the inverse rotation to retrieve  $ROT(IDS + K1 + \pi + n1, K2) + K1$ . This is a flaw in Ahmed's analysis that will not permit the completion of authentication.

Another modification proposed by Ahmed et al. concerning the MixBits function has also a very weak effect on overcoming the weakness of both random numbers n1 and n2 equal to zero. In the original Gossamer protocol, the mix-bits function exists during the creation of the new IDS and Key values.

```

Z = MixBits (X, Y)

Z = X

FOR counter = 0 to 32

Z = (Z >> 1) + Z + Z + Y

ENDFOR

```

Figure 2.3 MixBits function (repeated)

Where X and Y are the input 96-bit numbers and Z is the final result of the MixBits function. The weakness identified by Ahmed et. al is that if both of the MixBits input values (n1 and n2 in the first run) are equal to 0 then the result of the function is also equal to 0. As a result all transformations are dependent on the Key values, the IDS and Pi. This weakens the effective security of the Gossamer Protocol. Ahmed et al proposed the following modification:

```

Z = MixBits (X, Y)

Z = X

FOR counter = 0 to 32

Z = (Z+counter) + Z + Z + Y

ENDFOR

```

Figure 2.4 Modified MixBits Function

It is obvious that in a case where both n1 and n2 numbers are equal to zero then the result of the MixBits function will be always the sum of numbers 1 to 32 which is 528. The proposed attack on the MixBits functions where n1 and n2 are 0 has been rectified but now the first attack proposed can be still performed but using the value of 528 instead of 0 at the first call of the MixBits function within the Protocol (n3 calculation) and the result can be applied to the subsequent formulae to generate keys and messages.

Temporarily as a solution to the first attack it is recommended not to allow both random generated numbers to hold a value of zero at the same time. This verification should be performed by the PRNG function before the values are forwarded to the reader.

An altered Gossamer Protocol is suitable as a mechanism for authenticating Resource Limited Devices. The reader-tag relation is close to the master-slave one in the Infrastructure WSN scenario (see section 3.1). The main difference is the fact that a RFID tag is triggered by the reader, where in the IWSN all slaves will periodically initiate the communication. This difference is not significant in terms of the Gossamer specification as the 'Hello' message send by the reader to initiate the communication does not carry any protocol-specific data, thus can be discarded without any effect. It has to be pointed out that the Gossamer protocol was designed to be implemented in hardware but the simplicity of the mathematical operations renders it easily implementable in software on the reference platform nRF9E5 (see section 3.4). In consequence, this protocol is chosen for the implementation and further performance analysis.

## **Ultralightweight RFID Protocol with Mutual Authentication (UMA-RFID)**

Shortly after the Gossamer Protocol was published Lee at al. proposed UMA-RFID alternative (Lee et al. 2009). The protocol is very similar to the Gossamer specification but simplified to use only bitwise operations (XOR, OR, AND) and a left bitwise rotation function ROT. Each tag contains a static identifier ID, pseudonym called the dynamic temporary identifier (IDT) and a secret key (K). All variables are 128-bits long and shared between the tag and the back-end database accessible by the reader (secure channel assumed). The reader is assumed to be capable of generating random number (N). The protocol consists of two stages: Authentication Phase and Update Phase.

Authentication Phase: the reader sends a request message and the tag replies with a temporary identifier (IDT). The reader searches the database to find a secret key K<sub>i</sub> corresponding to the IDT received, generates random number N<sub>i</sub> and calculates messages A<sub>i</sub> and B<sub>i</sub> as follows:

$$A_i = K_i \oplus N_i$$

$$B_i = ROT(K_i, K_i) \oplus ROT(N_i, N_i)$$

The messages are concatenated and sent to the tag. Upon receiving these messages the tag obtains  $N_i$  from message  $A_i$  and calculates message  $B_i$  in the same way as the reader previously. Then message  $B_i$  is compared with  $B_i$ . If they are the same then the reader is authenticated and the tag generates reply message  $C_i$  as follows:

$$C_i = (K_i \vee ROT(N_i, N_i)) \oplus (ROT(K_i, K_i) \wedge N_i)$$

The message is sent to the reader and the reader calculates a local copy and verifies the correctness. After successful verification the tag is authenticated.

• Updating phase: the tag performs this phase after authenticating the reader. The updating on the reader side is done upon successful authentication of the tag. Both sides use the following equations to update IDT<sub>i+1</sub> and K<sub>i</sub>:

$$IDT_{i+1} = K_i \oplus ROT(N_i, N_i)$$

$$K_i = ROT(K_i, K_i) \oplus N_i$$

Peris-Lopez et al. analysed the UMA-RFID protocol (Peris-Lopez et al. 2009) and found serious weaknesses in the scheme which led to ID Disclosure, Full Disclosure and De-Synchronization attacks. Peris-Lopez et al. described 5 attacks: ID-disclosure attack, two passive Full Disclosure attacks and two active De-Synchronization attacks. The most significant Full Disclosure attack allowing cloning of the tag to be performed after eavesdropping of only two consecutive runs of the protocol and requires only computing XOR among some of the messages transmitted over the radio channel.

# SQUASH – A New MAC with Provable Security Properties for Highly Constrained Devices Such as RFID Tags

Adi Shamir proposed an authentication mechanism based on a challenge-response scheme and Message Authentication Code (MAC) called SQUASH (short for SQUare-hASH) specifically for Resource Limited Devices (Shamir 2008). The proposed challenge-response scheme allows tag-to-reader authentication and does not address the ID disclosure issue. The document focuses on describing a strong one-way hashing function (H) performed by the tag upon receiving a random challenge message (R). The MAC is computed with (R) and secret key (S) as inputs:

$$MAC = H(S, R)$$

The reader shares the secret key S and performs the same calculation upon receiving the MAC to validate if a tag is legitimate. The author made an interesting observation that most of the standard one-way hash functions such as SHA-1 (Eastlake & Jones 2001) are primarily designed to be collision resistant as their main area of usage concerns digital signatures. The requirement for collision resistance typically adds complexity to the algorithm. Since a collision is not a security threat in

a challenge-response scheme, the author proposed an algorithm based on the Rabin encryption scheme (Rabin 1979). In the Rabin scheme the ciphertext (c) is computed as  $c = m^2 \pmod{n}$ , where (m) is a message and (n) is a product of at least two unknown prime factors. Shamir has shown how the calculation can be simplified using a step-by-step process that has no adverse effects on the strength of the security and has proposed a hardware implementation using mixing function (M) applied to the secret and challenge (S, R) and then the SQUASH function SQUASH(M(S,R)) as follows:

- 1. Start with j which is the index at lower end of the desired extended window of t + u bits, and set carry to 0.

- 2. Numerically add to the current carry (over the integers, not modulo 2) the k products of the form  $mv * m_{j-v(mod \ k)}$  for v = 0, 1, 2, ..., k 1.

- 3. Define bit cj as the least significant bit of the carry, set the new carry to the current carry right-shifted by one bit position, and increment j by one.

- 4. Repeat steps 2 and 3 t + u times, throw away the first u bits, and provide the last t bits as the response to the challenge.(Shamir 2008)

The proposed SQUASH-128 hash function uses a modulus  $2^{1277}-1$ , a 64-bit key S and a 64-bit challenge R to produce a 32-bit response. The security of this scheme was questioned by Ouafi & Vaudenay, who discovered a key recovery attack known as "known random coins attack" against the Rabin scheme using 1024 chosen challenges (Ouafi & Vaudenay 2009). The "known random coins attack" allows an adversary to request many encryptions of the same plaintext and in consequence get the random coins. The attack is only effective if a linear mixing function is used, thus the security of SQUASH is still regarded as strong, assuming that a non-linear mixing function is used.

#### **SPINS - Security Protocols for Sensor Networks**

Perrig et al. proposed a security mechanism consisting of two blocks: Secure Network Encryption Protocol (SNEP) and µTESLA (Perrig et al. 2002). SNEP's security goals are data confidentiality, mutual authentication and the evidence of data freshness<sup>2</sup>. µTESLA provides a mechanism for an authenticated broadcast.

According to the authors SNEP achieves previously mentioned security goals with a very low communication overhead of only 8 bytes per message. SNEP ensures semantic security using two counters  $C_A$  and  $C_B$  shared by the communicating nodes. These counters are further used by the block cipher in counter mode. Counters do not have to be attached to messages but Perrig et al. described a mechanism of counter synchronization. The mutual authentication is achieved through the usage of a MAC function. Both communicating nodes A (sender) and B (receiver) share a master secret key  $X_{AB}$  used to derive keys through a pseudorandom function. It has to be noted that the authors advised deriving different

\_

<sup>&</sup>lt;sup>2</sup> Data freshness ensures that the data received is fresh and the adversary cannot replay old messages.

<sup>&</sup>lt;sup>3</sup> Semantic security ensures that an eavesdropper is not able to deduct any information about the plaintext even after analysis of multiple encryptions of the same plaintext.

key sets for MAC and encryption. Each key set consists of two keys - one for each direction of the communication.

Encryption keys:

$$K_{AB} = F(X_{AB})$$

$$K_{BA} = F(X_{AB})$$

MAC keys:

$$K'_{AB} = F(X_{AB})$$

$$K'_{BA} = F(X_{AB})$$

The sender node A encrypts (symmetric block cipher) the data using K<sub>AB</sub> and C<sub>A</sub>:

$$E = F_{crvpt}(K_{AB}, C_A)$$

The encrypted result is then used by the MAC function in the following manner:

$$MAC(K_{AB} C_A \parallel E)$$

Finally the sender node sends the message:

$$A \rightarrow B: F_{crvpt}(K_{AB}, C_A), MAC(K'_{AB}, C_A \parallel F_{crvpt}(K_{AB}, C_A))$$

This scheme does not provide data freshness. A solution for this issue is provided by the usage of a random number  $N_A$  and a request message  $R_A$  send by the node A:

$$A \rightarrow B: N_A, R_A$$

The Receiving Node B responds with an encrypted message and a MAC function with a cryptographic nonce  $N_A$  as one of the inputs:

$$B \rightarrow A: F_{crypt}(K_{BA}, C_A), MAC(K'_{BA}, N_A \parallel C_B \parallel F_{crypt}(K_{BA}, C_B))$$

Upon receiving the message and MAC verification the node A is sure that the node B generated the message using the cryptographic nonce supplied in a request message.

SNEP messages require synchronized counters on both sides of the communication. If the synchronization is lost for example due to lost messages, counter values can be re-synchronized through the following messages:

$$A \rightarrow B$$

:  $C_A$   $B \rightarrow A$ :  $C_B, MAC(K'_{BA} C_A \parallel C_B)$   $A \rightarrow B$ :  $MAC(K'_{AB}, C_A \parallel C_B)$

The concept of  $\mu$ TESLA was based on a TESLA protocol providing a mechanism of an authenticated broadcast (Perrig et al. 2001). This scheme achieves asymmetry through a delayed disclosure of symmetric keys rather than using computationally expensive Public Key Cryptography. The TESLA proposal is not suitable for implementation within a constrained devices environment. In order to adapt it for the Wireless Sensor Networks the following issues were addressed:

- TESLA authenticates the initial packet with a digital signature. The computation of a digital signature is too expensive on sensor nodes so µTESLA uses only a symmetric mechanism.

- Standard TESLA discloses the key for the previous intervals with every packet. Since this generates too much overhead  $\mu$ TESLA discloses the key once for each pre-defined epoch.

- Sensor nodes are not able to store an entire one-way key chain in the memory. This is addressed in µTESLA by limiting the number of authenticated senders.

The  $\mu$ TESLA requires that all receiving nodes are loosely time synchronized with the base station. In order to send an authenticated broadcast, the base station computes a MAC using the packet and a key which is secret at that point in time. The receiving node stores the packet in the buffer in order to validate its authenticity later when the base station broadcasts the verification key. Each MAC is a key of a key chain, generated by applying a one-way hash function. A successive key is generated by applying the hash function on the previous key. The time synchronization can be achieved by the means of the SNEP protocol. The protocol consists of the following phases:

- Sender setup the sender node generates a one-way key chain by successively applying one-way hash function.

- Broadcasting authenticated packets the time is divided into inform intervals. The sender associates each key in the key chain with one particular interval and uses this key to compute MAC of all packets sent in that interval. The key  $K_i$  is disclosed after a delay which is greater than a few time intervals and has to be greater than a message round-trip time between the sender and the receivers.

- Bootstrapping a new receiver each receiver needs to authenticate one key in the one-way key chain which allows it to commit to the entire chain: further keys will be calculated using one-way hash function. The receiver needs to be loosely time synchronized with the sender and has to know the key disclosure schedule. Both of these requirements are fulfilled as follows: the Receiver node sends a request message containing a random number  $N_R$  and the Sender replies with a message containing its current time  $T_S$ , the key  $K_i$  used in the past interval i, the starting time of this interval  $T_{int}$  and the key disclosure delay  $\delta$ . These values are sent with clear

text along with a MAC calculated using these values, the random number  $N_R$  and shared secret key  $K_{MS}$ :

$$B \to A \colon N_R$$

$$A \to B \colon T_S \parallel K_i \parallel T_i \parallel T_{int} \parallel \delta$$

$$A \to B \colon MAC(K_{MS}, N_R \parallel T_S \parallel K_i \parallel T_i \parallel T_{int} \parallel \delta)$$

• Authenticating broadcast packets – upon receiving a message the receiver needs to make sure that this packet is safe by verifying if the key used to compute the MAC was not disclosed yet. This can be achieved thanks to loose time synchronization between the sender and the receiver. When a node receives a new key  $K_i$  it computes the one-way hash function on the previous key  $K_v$  in order to verify the correctness of  $K_i$ . If the check was successful then a node can authenticate all packets which arrived in the time interval of  $K_i$ .

Perrig et al. did not specify exactly which encryption algorithm should be used in SNEP, or which one-way hash function should be used by  $\mu$ TESLA, or indeed which Random-number generation should be used in both protocol blocks. However, Perrig et al. provide example functions for the experimental implementation. In order to tackle the issue of limited code space and RAM size all cryptographic primitives are based on a modified subset of the RC5 encryption algorithm (Rivest 1995).

The  $\mu$ TESLA's main disadvantage is the need for an initial unicast-based parameter distribution. This issue has been addressed by Liu & Ning in the Multi-Level  $\mu$ TESLA specification (Liu & Ning 2004). The scheme provides a way to predetermine and broadcast the initial parameters. Additionally, Multi-Level  $\mu$ TESLA introduces a multi-level key chain scheme which removes the need for very long key chain. The authors claim that the key chain commitment distribution mechanism described in their document improves the survivability of the scheme against message loss and Denial Of Service (DOS) attacks.

Since the SPINS specification does not propose exact cryptographic primitives to be used no security weaknesses were identified in the scheme to the knowledge of the author. However, several papers were published addressing efficiency and key management issues found in SNIPS (Liu & Ning 2004), (Yu-Long et al. 2007), (Hegazy et al. 2007).

Both of the SPINS schemes suffer from using Pseudo-Random Number Generator (PRNG) engines not only on the base station side but also on the sensors. Perrig et al. suggested that sensor nodes may draw random numbers from the actual sensor readings. However, the Analog-to-Digital Converters (ADCs) which are sometimes only 8 or 10-bit wide may not be able to provide random values in a magnitude large enough for cryptographic usage. Thus a resource expensive PRNG functions need to be implemented within a limited sensor node code space.

Due to a high computational overhead on the sensor node side, the SPINS implementation was not considered during this MSc project.

## 2.3 Encryption

Bruce Schneier said that "Cryptography is the art and science of keeping messages secure" (Schneier 1996). A message (referred to as a plaintext) undergoes a process of hiding its substance (encryption) and converting it into a non-meaningful gibberish (ciphertext or cipher) that can be sent over an insecure communication channel. The process of retrieving a plaintext from a ciphertext received is referred to as decryption.

The general rule followed in modern cryptography states that the security of the system cannot rely on the secrecy of its components (security by obscurity) – the secrecy must reside entirely in the encryption key. This principle was stated by Auguste Kerchoff in the nineteenth century (Menezes et al. 1997), who assumed that a cryptanalyst has a complete knowledge of the algorithm and implementation. An algorithm that has its security based on keeping its foundations secret is called restricted. Such a security system can be compromised through an information leak, reverse engineering, etc. Quality control and standardisation cannot be maintained.

The most common type of cryptography is the Secret-Key Cryptography (symmetric cryptography), where a message 'M' gets encrypted with encryption function E, using a key 'k' to generate a ciphertext 'c'. Therefore, c = E(k,M). The decryption function D should provide a way to recover the plaintext 'p' using shared secret 'k', such that p = D(k,c).