### **Accepted Manuscript**

# Journal of Circuits, Systems and Computers

Article Title: Performance Investigation of FinFET Based MO-CCII and its appli-

cations: Resistor-less Multi-Function Bi-quadratic Filter and Balanced

Modulator

Author(s): Mohd Yasir, Mohammad Samar Ansari

DOI: 10.1142/S0218126620501753

Received: 20 October 2018

Accepted: 18 November 2019

To be cited as: Mohd Yasir, Mohammad Samar Ansari, Performance Investigation of Fin-

FET Based MO-CCII and its applications: Resistor-less Multi-Function Bi-quadratic Filter and Balanced Modulator, *Journal of Circuits, Systems*

and Computers, doi: 10.1142/S0218126620501753

Link to final version: https://doi.org/10.1142/S0218126620501753

This is an unedited version of the accepted manuscript scheduled for publication. It has been uploaded in advance for the benefit of our customers. The manuscript will be copyedited, typeset and proofread before it is released in the final form. As a result, the published copy may differ from the unedited version. Readers should obtain the final version from the above link when it is published. The authors are responsible for the content of this Accepted Article.

## Accepted manuscript to appear in JCSC

June 24, 2019 12:33 WSPC/INSTRUCTION FILE "Yasir FinFET CCII Paper"

Journal of Circuits, Systems, and Computers © World Scientific Publishing Company

# Performance Investigation of FinFET Based MO-CCII and its applications: Resistor-less Multi-Function Bi-quadratic Filter and Balanced Modulator

Mohd Yasir\*

Z. H. College of Engineering & Technology, Aligarh Muslim University, Aligarh, UP, 202002, India \*myasir024@gmail.com

Mohd. Samar Ansari§

Athlone Institute of Technology,

Dublin Road, Athlone, Co Westmeath, Ireland

§ mdsamar@gmail.com

Received (20 October 2018) Revised (Day Month Year) Accepted (Day Month Year)

This paper presents an optimal design of a high-performance multi output secondgeneration current conveyor (MO-CCII) based on 20nm FinFETs. Proposed MO-CCII has very low port X impedance and very high port Y impedance. The performance of the CCII has been thoroughly investigated in terms of DC, AC and transient characteristics of terminal voltages and branch currents and frequency response of port impedances. CCII shows the excellent high-frequency response of voltage as well as current transfer gains. The 3dB BW of voltage and current transfer gains are 11.2GHz and 11GHz respectively. CCII provides excellent performance over its CMOS counterpart. Also, a resistor-less multi-function bi-quadratic filter is proposed. The filter depends on two CCIIs, a capacitor and does not require any resistors. It has three inputs and one output and realizes low-pass, high-pass and band-pass filters from a similar setup. FinFETs in the linear region are utilized as variable resistor to control filter properties. Nevertheless, the proposed filter has two floating capacitors which can be effortlessly realized in these days' integrated circuit advancements. Also, a balanced modulator is proposed utilizing the proposed FinFET based CCII and FinFET transistors only. Balanced modulator's frequency of operation obtained is in GHz range.

Keywords: Balanced Modulator, Current Conveyor, Current Mode Circuits, FinFET, Multi-Function Biquadratic Filter

#### 1. Introduction

The ongoing tremendous progress of semiconductor fabrication technology has permitted speed trends in the shrinkage rate of integrated circuits' (IC's) die area.

\*Z. H. College of Engineering & Technology, Aligarh Muslim University, Aligarh, India

#### 2 M. Yasir et al.

As per,<sup>1</sup> in 2017, there was created a chip in 10nm CMOS process node with the thickness of 100million transistors per  $1mm^2$ . Such an integration density brings extraordinary improvement of computational power per area. However, this pattern brings additional disadvantage, as downscaled process node endures from the random fluctuation of process parameters, voltage and temperature sensitivity (PVT) along with various samples on a wafer.<sup>2-4</sup>

With the requirement of highly down-scaled transistors in state-of-the-art ICs, lower power consumption, high performance and battery operated systems, CMOS circuits faced many challenges like Short Channel Effects (SCEs), process variations, etc.<sup>5</sup>

The techniques used for low power design are Self-Cascode topologies, MOS transistors operating in the sub-threshold region,  $gm/I_D$  approach, Bulk-Driven (BD) MOS transistors, Dynamic-Threshold MOS (DTMOS) transistors, *etc.* But these techniques provide low power design for lower frequencies and lower speed.<sup>6–9</sup>

Below 22nm transistor technology, FinFET devices become the prominent alternative to the Bulk CMOS as they can easily be integrated with the CMOS ICs and reduce SCEs. Also, they can provide better high frequency response as well as higher speed when compared with CMOS.

Introduction of multi-Gate devices such as FinFETs created a revolution in the VLSI industry. As bulk CMOS faces many SCEs when scaled down below 22nm transistor technology, it becomes necessary to have a new device which can reduce these SCEs. Some of the SCEs are Drain Induced Barrier Lowering (DIBL), Gate Induced Drain Leakage (GIDL), velocity saturation, hot carrier effect, etc. FinFETs, on the other hand, can restrict these SCEs because of better Gate control over the drain current  $(I_D)$  to provide lower voltage and low power operation of the device. Also, FinFET based devices are much faster and consume lower dynamic as well as static power when compared with bulk CMOS. In this paper, 20nm PTM model of FinFET has been used, which is discussed in.<sup>10</sup>

In the course of recent years, there has been a developing enthusiasm for Current-Mode (CM) circuits. In contrast with traditional Voltage-Mode (VM) signal processing, there are various advantages to pick up from CM circuits, for example, low voltage operation, great frequency performance, substantial dynamic range, higher bandwidth (BW), simpler architectures, lower power consumption, etc. In the expansion, innovative solutions gave by CM approach help designers to take care of the issues of the circuit design in modern technologies. Nowadays, extensive research has been done in this field to use various CM active building blocks and substitute VM circuits by CM ones. In recent years many applications based on CM circuits have been implemented like oscillators, filters, instrumentation amplifiers, impedance converters, etc. <sup>11–15</sup> Clearly, the most utilized CM active building blocks are current conveyors (CCs). <sup>16</sup>

There is a need for a basic building block that can be used to implement the different type of analog functions. One such block is Operational Amplifier (OPAMP)

Performance Investigation of FinFET Based MO-CCII and its applications

that can be used to implement a large number of analog functions. It is a VM circuit and has suffered from the constant gain-BW product, poor slew rate, poor high-frequency response, lower BW, etc. CCII can be a real competitor of OPAMP, because it is a CM device, and has many advantages over OPAMP like higher BW, better slew rate, lower power consumption, larger dynamic range, etc.

Initially, analog building blocks like OPAMPs, Operational Transconductance Amplifiers (OTAs), CCs, etc. were designed using BJTs. BJTs have many advantages like large gain-BW product, better high-frequency performance, better voltage gain, high current density, high driving capability, etc. On the other hand BJTs have many disadvantages, like large associated noise, radiation effects, consume large power, very low thermal stability, etc. But as circuit complexity starts increasing BJTs consume very large power. So, IC industry started searching for other devices and came up with MOSFETs. Because they produce very low noise, better thermal stability, simpler to fabricate, higher integration density, and consume very low power. But as technology scaling goes beyond 22nm technology node CMOS implementation of ICs also affected by many effects like SCEs, sub-threshold leakage, etc., some of the new techniques like Carbon Nano Tube Field Effect Transistors (CNTFETs), FinFETs, Tunnel FETs (TFETs), etc. were developed. But IC industry mainly used FinFETs as an alternative to CMOS, because they are compatible with CMOS process and by adding a small number of steps in CMOS process flow, FinFET based circuits can be implemented easily.

This paper is organized into seven sections. Section II presents an overview of FinFET devices. Section III highlights important aspects of a current conveyor. In Section IV performance of the FinFET based CCII has been investigated using HSPICE. Section V presents theory and simulation results of MO-CCII based multifunction bi-quadratic filter. In section VI, theory and simulation results of proposed balanced modulator are present followed by conclusions drawn in Section VII.

#### 2. FinFET Overview

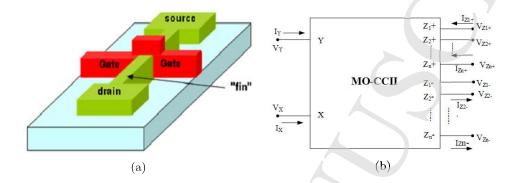

Difficulty in the fabrication of Double Gate MOSFET (DGMOS), because of the alignment problem of front and back gates, there is a need for an alternative technology which can overcome this problem. The development of FinFET (Fin-Shaped Field Effect Transistor) overcome these fabrication problems of DGMOS. The gate region covers the body from three sides. FinFET is a Non-planar Multi-Gate device mounted on a Silicon on Insulator (SOI) substrate which reduces the off current  $(I_{OFF})$  to reduce static power consumption. The basic structure of FinFET is shown in Fig. 1a. Channel in FinFET is a semi-conducting fin which has a width w and height h, where w < h. The distance between source and drain of FinFET is known as fin length (L). Fin height  $(H_{FIN})$  and fin thickness  $(T_{FIN})$  are the main characteristics of a fin. The SOI substrate provides many advantages over Bulk CMOS like lower  $I_{OFF}$ , lower operating voltage, no drain current losses due to body effect, better control of gate voltage over  $I_D$ , smaller SCEs, higher transconductance (gm),

#### 4 M. Yasir et al.

Fig. 1: (a) Basic Structure of FinFET<sup>21</sup> (b) Symbolic representation of MO-CCII

ideal sub-threshold voltage. Therefore, FinFETs are easier to scale down physically as well as electrically when compared with Bulk CMOS. The effective width of the transistor is calculated using Eq. (1)

$$W_{eff} = n * (2 * H_{FIN} + T_{FIN}) \tag{1}$$

where n is the number of fins,  $H_{FIN}$  is fin-height and  $T_{FIN}$  is fin thickness. For 20nm PTM model of FinFET,  $T_{FIN}$  is 15nm and  $H_{FIN}$  is 28nm. FinFETs provide a road-map to scale down the feature size up to 7nm. <sup>17–19</sup>

A further advantage of the multi-sided gate is more drive current per unit area than Bulk CMOS—the height of the fin can be utilized to make a channel with a bigger effective volume than a planar device with a similar equivalent gate length. This converts into better effective performance. The additional performance capability of FinFETs can be utilized to accomplish higher frequency compared with a planar device for a given power budget.<sup>20</sup>

#### 3. Current Conveyor Overview

CCII has four ports namely X, Y, Z+ and Z- ports. X and Y ports are input ports and Z+ and Z- are output ports. It has a high input impedance port for voltage inputs, one low input impedance port for current input, and two high output impedance ports for current outputs.

CCII is a current mode device which delivers the current from input X port to the output Z+ and Z- ports with unity gain and voltage from Y port to X port with unity gain. CCII provides better high frequency response when compared with OPAMP. Therefore CCII has an edge over OPAMP for high-frequency applications. Because of its versatility, CCII is suitable for both VM as well as CM circuits. CCII has been used to implement precision rectifiers, capacitance multipliers, impedance converters, integrators, differentiators, filters, etc.<sup>22-29</sup> The symbol and transistor level diagram are shown in Fig. 1b and Fig. 2 respectively. The characteristic equa-

Performance Investigation of FinFET Based MO-CCII and its applications

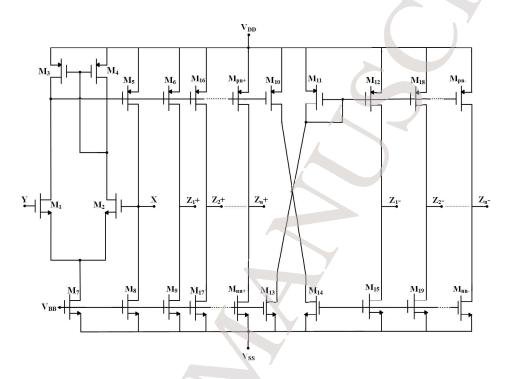

Fig. 2: Transistor Level Realization of MO-CCII

Table 1: PARAMETERS OF FinFET BASED MO-CCII (L=100nm for all transistors)

| Transistors | $M_1, M_2$ | $M_3, M_4$ | $M_5, M_6, M_{10}$ | $M_{16}$ | $M_7$ | $M_8, M_9$ | $M_{13}, M_{17}$ |

|-------------|------------|------------|--------------------|----------|-------|------------|------------------|

| No of Fins  | 2          | 4          | 45                 | 5        | 60    | 10         | 8                |

tion for CCII can be represented as follows.

$$\begin{bmatrix} I_Y \\ V_X \\ I_{Z\pm} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 \\ 1 & 0 & 0 \\ 0 & \pm 1 & 0 \end{bmatrix} \begin{bmatrix} V_Y \\ I_X \\ V_{Z\pm} \end{bmatrix}$$

(2)

where  $V_X$  and  $V_Y$  are the input voltages at X and Y ports respectively,  $I_Y$ , and  $I_X$  are input currents at Y and X ports and  $I_{Z\pm}$  are the output currents at Z± ports, and  $V_{Z\pm}$  are the voltages at Z± ports. Ideal CCII must have following properties.

(a) Infinite input impedance  $(Z_Y)$  at Y port for voltage inputs. (b) Zero input impedance  $(Z_X)$  at X port for current inputs. (c) Infinite output impedances  $(Z_{Z\pm})$  at  $Z\pm$  ports for current outputs. (d) Infinite BW. (e) Unity Voltage transfer gain between Y and X ports. (f) Unity Current transfer gains among X and  $Z\pm$  ports.

6 M. Yasir et al.

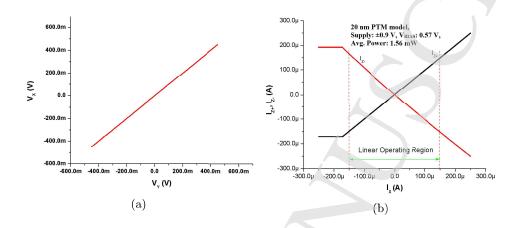

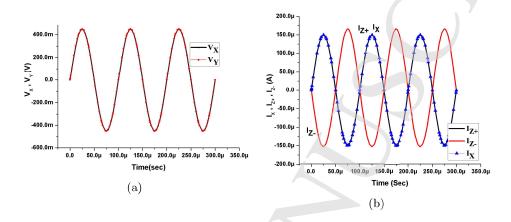

Fig. 3: (a) Voltage Transfer Characteristics between Y and X ports (b) Current Transfer Characteristics among the X, Z+ and Z- ports

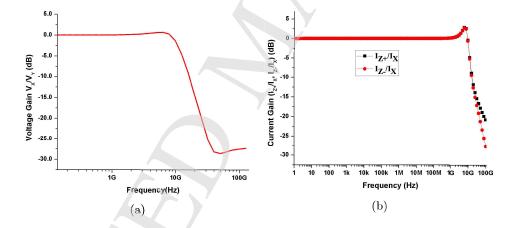

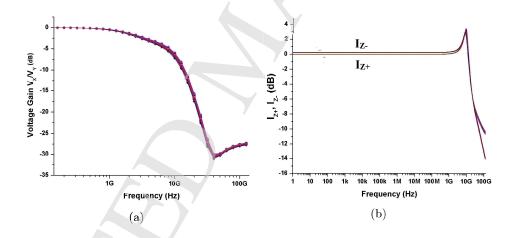

Fig. 4: (a) Frequency Response of Voltage Gain  $(V_X/V_Y)$  (b) Frequency Response of  $I_{Z+}$  and  $I_{Z-}$

#### 4. Performance Investigation of FinFET based MO-CCII

With the advent of FinFET, researchers made important analog as well as digital circuits<sup>19</sup> like OTAs and OPAMPs,<sup>30,31</sup> SRAMs,<sup>32,33</sup> ring oscillators,<sup>34</sup> Schmitt trigger,<sup>35</sup> etc. using these devices. But as far as author's knowledge, FinFET based architecture of CCII was first proposed in.<sup>36</sup> In this paper, an MO-CCII using 20nm FinFET has been designed and its performance is investigated using HSPICE. To ensure better cascading, input impedance for voltage input Y port must be very high, input impedance for current input X port must be very low and output

| June 24, 2019 | 12:33 | WSPC/INSTRUCTION FILE | "Yasir FinFET CCII |Paper"

Performance Investigation of FinFET Based MO-CCII and its applications

Fig. 5: (a) Transient Response of Voltage Follower between Y and X ports (b) Transient Response of Current Relationship among the X, Z+, and Z- ports

Fig. 6: (a) Monte Carlo analysis for Voltage Gain  $(V_X/V_Y)$  (b) Monte Carlo analysis for  $I_{Z+}$  and  $I_{Z-}$  using 2000 samples

impedance for current output Z± ports must be very high.

All simulations are done using HSPICE. FinFETs used in this paper are based on 20nm PTM models. Power supply voltages used are  $\pm 0.9V$  and biasing voltage used is 0.57V, for the proper operation of CCII. Average power dissipation is 1.56mW. The parameters of various transistors in the designed module are given in Table 1.

The DC characteristics of CCII are shown in Fig. 3. DC voltage transfer characteristics between ports Y and X are shown in Fig. 3a. A DC voltage is applied at Y terminal and the voltage at X terminal follows it linearly according to the characteristics.

1G

Frequency (Hz)

(a)

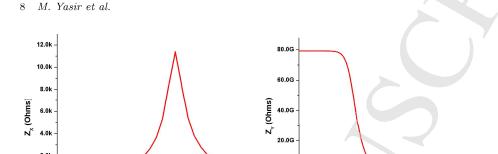

Fig. 7: (a) Frequency Response of Port X Impedance (b) Frequency Response of Port Y Impedance

0.0

10M 100M 1G 10G 100G

100k 1M

(b)

Frequency (Hz)

acteristic equation of CCII. The graph between  $V_Y$  and  $V_X$  shows linear behavior from -450mV to 450mV. Fig. 3b shows the current transfer characteristics among X, Z+ and Z- ports. A DC current is applied at X terminal of the CCII and shows good linear behavior among X, Z+, and Z- ports and shows linear behavior from  $-150\mu\text{A}$  to  $150\mu\text{A}$ .

AC characteristics of CCII are shown in Fig. 4. Fig. 4a shows the AC voltage transfer characteristics between  $V_X$  and  $V_Y$ . The 3dB BW of voltage transfer gain is 11.2GHz. Fig. 4b shows the AC current transfer characteristics. The 3dB BW obtained for current transfer gain is 11GHz.

Results of transient analysis of CCII are presented in Fig. 5. Fig. 5a shows the transient response of voltage follower action of the ports Y and X. It clearly shows that port X voltage follows the voltage at port Y. Fig. 5b shows the transient response of current transfer characteristics among port X and ports Z+ and Z-.

Monte Carlo analysis has been done on performance parameters (Voltage Gain and Current Gain). The independent parameter of  $H_{FIN}$  has been chosen and assumed to have independent Gaussian distribution with  $3\sigma$  variation of 10% with 2000 samples.  $^{37}$   $H_{FIN}$  has been taken because it has a major contribution to the effective width of fin of the transistor as given in (1). Monte Carlo analysis for voltage as well as current gain are shown in Fig. 6.

The port impedances of the device are shown in Fig. 7. Fig. 7a shows the frequency response of port X impedance.  $Z_X$  has a value of  $1.5K\Omega$  for a frequency of 2.5GHz. Ideally, the value of  $Z_X$  must be very low and the simulated results are also providing the quite low value of  $Z_X$ . Fig. 7b shows the frequency response of port Y impedance. For lower frequencies,  $Z_Y$  is  $79G\Omega$  and has a value of  $377K\Omega$  for a frequency of 2.5GHz. Ideally, port Y impedance must be very high and the simulated results are also providing the quite high value of  $Z_Y$ .

Performance Investigation of FinFET Based MO-CCII and its applications

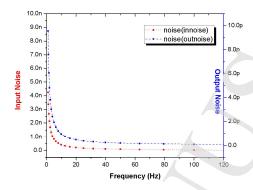

Fig. 8: Noise Analysis of DO-CCII with  $V_Y$  as input port

Total output noise is  $9.56pV/\sqrt{Hz}$  and equivalent input noise at  $V_Y$  is  $4.24nV/\sqrt{Hz}$  as shown in Fig. 8. Also, Table 3 shows the comparison of noise performance of the proposed MO-CCII with other state-of-the-art circuits. The proposed circuit can provide much better noise performance over the other circuits except. This significant improvement in noise performance is attributed to the smaller  $T_{FIN}$  of FinFETs. The flicker noise and its temperature dependence become smaller as  $T_{FIN}$  becomes lower than 30 nm (In this design, it is 15 nm). This effect comes into the picture because the smaller  $T_{FIN}$  provides relaxation of the vertical electrical field from channel to gate electrode. Therefore FinFET with smaller  $T_{FIN}$  is more attractive in designing analog circuits than bulk CMOS because of its excellent noise performance.

Table 2 shows the comparison of the performance of the proposed MO-CCII with other state-of-the-art circuits. The proposed circuit can provide much better performance in terms of high frequency response. The proposed MO-CCII provides a 3dB BW of 11GHz for currents while 11.2GHz voltage gain. Also, one can see from the table that the CCII in<sup>39</sup> provides 3dB BW of 195MHz for current gain while 377MHz for voltage gain; similarly, the CCIIs in,<sup>40</sup>,<sup>41</sup>,<sup>42</sup> and<sup>43</sup> also providing 3dB BW for current as well as voltage gains in MHz range only.

# 5. Multi-Function Bi-quadratic Filter based on FinFET based MO-CCII

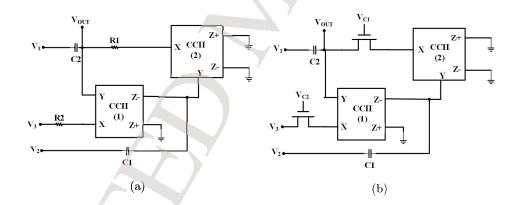

A VM multi-function bi-quadratic filter based on proposed MO-CCII which does not need any resistors employing CCII as an active building block is proposed. Fig. 9a shows the circuit proposed in<sup>47</sup> and Fig. 9b shows the implementation of Fig. 9a using voltage controlled resistor by making use of a single transistor in linear region as a variable resistor to control filter properties electronically. Two CCIIs, two capacitors and two FinFETs working in the linear region are utilized to realize bi-quadratic BP, LP, and HP transfer functions (TFs) all together with a similar

June 24, 2019 12:33 WSPC/INSTRUCTION FILE "Yasir FinFET CCII Paper"

10 M. Yasir et al.

Table 2: Performance Comparison of the Proposed MO-CCII with State-of-the-Art Circuits

| Performance                    | Proposed            | 39                 | 40            | 41                  | 42                 | 43                 |

|--------------------------------|---------------------|--------------------|---------------|---------------------|--------------------|--------------------|

| Parameters                     | MO-CCII             |                    |               |                     |                    |                    |

| Process                        | 20nm FinFET         | $0.18 { m m}$      | $0.13 { m m}$ | 0.18m               | $0.5 \mathrm{m}$   | 0.35m              |

| Technology                     | FinFET              | CMOS               | CMOS          | CMOS                | CMOS               | CMOS               |

| Supply Voltage (V)             | $\pm 0.9$           | ±0.9               | 1.5           | $\pm 0.5$           | $\pm 0.75$         | $\pm 1.65$         |

| Power Dissipation (mW)         | 1.56                | 0.45               | 1.5           | 120                 | 1.62               | 1.3                |

| DC Current Range (A)           | $\pm 150$           | ±80                | ±20           | $\pm 24000$         | ±100               | ±3000              |

| DC Voltage Range Y (mV)        | $\pm 450$           | $\pm 350$          | Rail to Rail  | $\pm 240$           |                    | -1.43  to  +1.1    |

| 3dB BW for $I_{Z+}$ , $I_{Z-}$ | $11 \mathrm{GHz}$   | $195 \mathrm{MHz}$ | 99MHz         | $30.2 \mathrm{MHz}$ | $100 \mathrm{MHz}$ | $915 \mathrm{MHz}$ |

| 3dB BW for $V_X/V_Y$           | $11.2 \mathrm{GHz}$ | 377MHz             | 94MHz         | $36 \mathrm{MHz}$   | -                  | 810MHz             |

Table 3: Noise Performance Comparison of the Proposed MO-CCII with State-of-the-Art Circuits

| Noise Performance<br>Parameters | Proposed<br>MO-CCII  | 44                           | 45                        | 46                            | 42                          | 36                           |

|---------------------------------|----------------------|------------------------------|---------------------------|-------------------------------|-----------------------------|------------------------------|

| Output Noise                    | 9.56 pV/ $\sqrt{Hz}$ | $4.51~\mathrm{nV}/\sqrt{Hz}$ | $23 \text{ nV}/\sqrt{Hz}$ | $0.5~\mu\mathrm{V}/\sqrt{Hz}$ | $4.1~\mathrm{nV}/\sqrt{Hz}$ | $9.56~\mathrm{pV}/\sqrt{Hz}$ |

Fig. 9: (a) Block Diagram of Filter reported in  $^{47}$  (b) MO-CCII based Multi-Function Filter Implementation of Fig. 9a using voltage controlled resistor

arrangement. The proposed VM multi-function filter utilizes two floating capacitors which can be effectively realized in these days' IC technology.  $^{48}$

The transfer function for the proposed circuit can be obtained using direct analysis and can be expressed as follows.

$$V_0 = \frac{s^2 R_1 R_2 C_1 C_2 V_1 + s R_2 C_1 V_2 + V_3}{s^2 R_1 R_2 C_1 C_2 + s R_2 C_1 + 1}$$

(3)

Performance Investigation of FinFET Based MO-CCII and its applications

Table 4: Performance Characteristics of the proposed filter

| Performance         | Supply Voltage | Total Power      | Frequency of    | Bandwidth |

|---------------------|----------------|------------------|-----------------|-----------|

| Factor              | $V_{DD}$ (V)   | Dissipation (mW) | operation (GHz) | (MHz)     |

| GHz frequency range | ±0.9           | 3.26             | 2.1             | 720       |

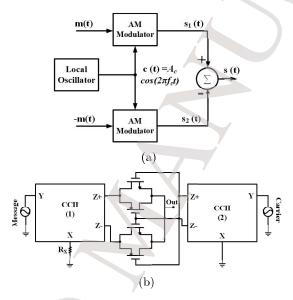

Fig. 10: (a) Block Diagram of a Balanced Modulator (b) MO-CCII Based Balanced Modulator Implementation of Fig. 10a

The three TFs obtained using (3) are: (a) Second-order low-pass filter can be obtained using  $V_1=V_2=0$  (grounded), (b) Second-order band-pass filter can be obtained using  $V_1=V_3=0$  (grounded), and (c) Second-order high-pass filter can be obtained using  $V_2=V_3=0$  (grounded). Therefore the natural frequency  $(\omega_0)$  and quality factor Q can be given as:

$$\omega_0 = \frac{1}{(R_1 R_2 C_1 C_2)^{1/2}} \text{ and } Q = (\frac{R_1 C_2}{R_2 C_1})^{1/2}$$

(4)

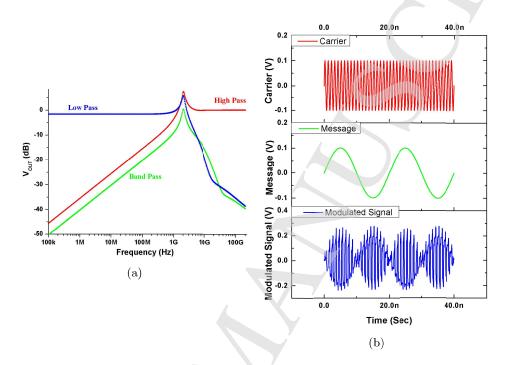

Fig. 11a shows the filter responses for the proposed filter. Component values taken are  $C_1 = 0.005 \text{pF}$  and  $C_2 = 0.05 \text{pF}$ . The frequency of operation obtained for the filter is 2.1GHz. The total power consumed by the multi-function filter is 3.26mW. Table 4 shows the performance characteristics of the proposed filter in GHz frequency range.

12 M. Yasir et al.

Table 5: Performance Characteristics of the proposed balanced modulator

| Performance         | Supply Voltage | Average Power    | THD   | Message Signal  | Carrier         |

|---------------------|----------------|------------------|-------|-----------------|-----------------|

| Factor              | $V_{DD}$ (V)   | Dissipation (mW) |       | Frequency (MHz) | Frequency (GHz) |

| GHz frequency range | ±0.9           | 2.97             | 4.41% | 50              | 1               |

#### 6. Balanced Modulator

A Balanced Modulator might be characterized as a circuit in which two non-linear devices are associated in a balance mode to deliver a Double Sideband Suppressed Carrier (DSBSC) signal. The balanced modulators are utilized to suppress the undesirable carrier in an AM wave. The carrier and modulating signals are connected to the inputs of the balanced modulator and the DSB signal with the suppressed carrier can be obtained at the output of the balanced modulator. In this manner, the output comprises the upper and lower sidebands only. The general block diagram of a balanced modulator is shown in Fig. 10a and its MO-CCII implementation is shown in Fig. 10b.<sup>49</sup>

The simulation results for the proposed balanced modulator are shown in Fig. 11b. The message signal has a frequency of 50MHz and the carrier frequency is 1GHz. The Total Harmonic Distortion (THD) in the output comes out to be 4.41%. The average power consumed by the balanced modulator is 2.97mW. Table 5 comprises of the balanced modulator's performance characteristics for its application in GHz frequency range.

Although, the values of  $Z_{Y1}$  and  $Z_{Y2}$  are quite high at 1GHz but they are not infinite. Therefore, the output performance of the proposed balanced modulator operating at 1GHz gets affected and the THD becomes 4.41% otherwise it will remain much lower than this value.

#### 7. Conclusion

In this paper, the performance analysis of 20nm FinFET based MO-CCII has been done using HSPICE. DC as well as AC analysis shows great coherence between the theoretical and simulated behavior of the device. The DC voltage range for the proposed CCII is -450mV to 450mV and AC analysis shows 3dB BW of currents and voltage gains as 11GHz and 11.2GHz respectively. The port impedances of the device also show nearly ideal values. Simulation results show that FinFET based approach has an edge over CMOS based approach beyond 22nm channel length. Also, a VM multi-function bi-quadratic filter capable of simultaneous realization of LP, BP and HP TFs from the same circuit topology is proposed. It depends on two CCIIs, two floating capacitors which can be easily realized in these days' IC process and two FinFETs working as a variable resistor. The proposed balanced modulator works perfectly in GHz frequency range. It utilized proposed FinFET based CCIIs and FinFETs only. It is expected that the proposed circuits will be valuable in numerous fields, for example, signal processing, control engineering, and

| June 24, 2019 | 12:33 | WSPC/INSTRUCTION FILE | "Yasir FinFET CCII | Paper"

Performance Investigation of FinFET Based MO-CCII and its applications

Fig. 11: (a) Filter Responses of Multi-function Bi-quadratic filter using MO-CCII (LP response shown in blue, BP response shown in green, and HP response shown in red) (b) Results for the proposed balanced modulator (DSBSC modulated signal shown in blue, message signal with 50MHz frequency shown in green, and carrier signal with 1GHz frequency shown in red

broadcast communications.

#### References

- 1. R. Courtland, Intel now packs 100 million transistors in each square millimetre https://spectrum.ieee.org/nanoclast/semiconductors/processors/intel-now-packs-100-million-transistors-in-each-square-millimeter.html., Accessed: 2018-05-29.

- 2. V. Stopjakova, M. Rakus, M. Kovac, D. Arbet, L. Nagy, M. Sovcik and M. Potocny, Ultra-low voltage analog ic design: Challenges, methods and examples, *Radioengineering* 27(1) (2018) 171–185.

- 3. M. Rakus, V. Stopjakova and D. Arbet, Analysis of bdmos and dtmos current mirrors in 130 nm cmos technology, *Advances in Electrical and Electronic Engineering* **16**(2) (2018) 226–232.

- 4. M. Rakús, V. Stopjaková and D. Arbet, Design techniques for low-voltage analog integrated circuits, *Journal of Electrical Engineering* **68**(4) (2017) 245–255.

- 5. D. J. Frank, R. H. Dennard, E. Nowak, P. M. Solomon, Y. Taur and H.-S. P. Wong, Device scaling limits of si mosfets and their application dependencies, *Proceedings of*

| June 24, 2019 | 12:33 | WSPC/INSTRUCTION FILE | "Yasir FinFET CCII | Paper"

14 M. Yasir et al.

the IEEE 89(3) (2001) 259-288.

- E. Tlelo-Cuautle and A. C. Sanabria-Borbon, Optimising operational amplifiers by evolutionary algorithms and gm/id method, *International Journal of Electronics* 103(10) (2016) 1665–1684.

- 7. F. Khateb, Bulk-driven floating-gate and bulk-driven quasi-floating-gate techniques for low-voltage low-power analog circuits design, AEU-International Journal of Electronics and Communications 68(1) (2014) 64–72.

- 8. V. Niranjan, A. Kumar and S. B. Jain, Low voltage flipped voltage follower based current mirror using dtmos technique, in *Multimedia, Signal Processing and Communication Technologies (IMPACT), 2013 International Conference on*, IEEE2013, pp. 250–254.

- K.-J. Baek, J.-M. Gim, H.-S. Kim, K.-Y. Na, N.-S. Kim and Y.-S. Kim, Analogue circuit design methodology using self-cascode structures, *Electronics Letters* 49(9) (2013) 591–592.

- S. Sinha, G. Yeric, V. Chandra, B. Cline and Y. Cao, Exploring sub-20nm finfet design with predictive technology models, in *Proceedings of the 49th Annual Design Automation Conference*, ACM2012, pp. 283–288.

- 11. A. Yesil, E. Yuce and S. Minaei, Inverting voltage buffer based lossless grounded inductor simulators, *AEU-International Journal of Electronics and Communications* 83 (2018) 131–137.

- 12. P. Supavarasuwat, M. Kumngern, S. Sangyaem, W. Jaikla and F. Khateb, Cascadable independently and electronically tunable voltage-mode universal filter with grounded passive components, *AEU-International Journal of Electronics and Communications* 84 (2018) 290–299.

- 13. S. Summart, C. Thongsopa and W. Jaikla, New current-controlled current-mode sinusoidal quadrature oscillators using cdtas, AEU-International Journal of Electronics and Communications 69(1) (2015) 62–68.

- 14. A. Yesil, F. Kacar and S. Minaei, New differential difference stage and its application to band-pass filter at 10.7 mhz with high quality factor, *AEU-International Journal of Electronics and Communications* **79** (2017) 74–82.

- 15. L. Safari and S. Minaei, A novel coa-based electronically adjustable current-mode instrumentation amplifier topology, AEU-International Journal of Electronics and Communications 82 (2017) 285–293.

- X. Li, W. Zhao, Y. Cao, Z. Zhu, J. Song, D. Bang, C.-C. Wang, S. H. Kang, J. Wang, M. Nowak et al., Pathfinding for 22nm cmos designs using predictive technology models, in Custom Integrated Circuits Conference, 2009. CICC'09. IEEE, IEEE2009, pp. 227–230.

- 17. T. Cui, J. Li, Y. Wang, S. Nazarian and M. Pedram, An exploration of applying gate-length-biasing techniques to deeply-scaled finfets operating in multiple voltage regimes, *IEEE Transactions on Emerging Topics in Computing* **6**(2) (2018) 172–183.

- 18. S. Sinha, B. Cline, G. Yeric, V. Chandra and Y. Cao, Design benchmarking to 7nm with finfet predictive technology models, in *Proceedings of the 2012 ACM/IEEE international symposium on Low power electronics and design*, ACM2012, pp. 15–20.

- 19. T.-J. King, Finfets for nanoscale cmos digital integrated circuits, in *Proceedings of the* 2005 IEEE/ACM International conference on Computer-aided design, IEEE Computer Society2005, pp. 207–210.

- 20. L. Schuth, Arm describes finfets in the real-world https://www.electronicsweekly.com/news/research-news/process-rd/arm-describes-finfets-real-world-2014-10/.html., Accessed: 2018-05-29.

Performance Investigation of FinFET Based MO-CCII and its applications

- 21. M. Yasir and M. Hasan, High performance compact finfet based inductive boost converter, in *International Conference on Instrumentation, Measurement, Circuits and Systems, IMCAS'14*, Dec 2014, pp. 15–17.

- 22. L. Safari, E. Yuce and S. Minaei, A new low-power current-mode mos only versatile precision rectifier, *AEU-International Journal of Electronics and Communications* 83 (2018) 40–51.

- A. Yesil, E. Yuce and S. Minaei, Grounded capacitance multipliers based on active elements, AEU-International Journal of Electronics and Communications 79 (2017) 243–249.

- A. Kumar and S. K. Paul, Current mode first order universal filter and multiphase sinusoidal oscillator, AEU-International Journal of Electronics and Communications 81 (2017) 37–49.

- 25. A. S. Sedra, The current conveyor: History and progress, in *Circuits and Systems*, 1989., IEEE International Symposium on, IEEE1989, pp. 1567–1571.

- S. Minaei, O. K. Sayin and H. Kuntman, A new cmos electronically tunable current conveyor and its application to current-mode filters, *IEEE Transactions on Circuits* and Systems I: Regular Papers 53(7) (2006) 1448–1457.

- B. Wilson, Recent developments in current conveyors and current-mode circuits, IEE Proceedings G (Circuits, Devices and Systems) 137(2) (1990) 63-77.

- 28. C. Thoumazou, F. Lidgey and D. Haigh, Analog integrated circuit design: The current mode approch, *London*, *UK: IEE* (1990).

- 29. A. S. Sedra and K. C. Smith, A second-generation current conveyor and its applications, *IEEE Transactions on circuit theory* 17(1) (1970) 132–134.

- 30. S. Ferwani, S. Khandelwal and S. Akashe, Diminution of dissipated power and leakage current by employing finfet based opamp for 45nm regime., *Journal of Active & Passive Electronic Devices* **10**(3-4) (2015) 185–195.

- 31. A. Nandi, A. K. Saxena and S. Dasgupta, Oxide thickness and s/d junction depth based variation aware ota design using underlap finfet, *Microelectronics Journal* **55** (2016) 19–25.

- 32. B. Raj, A. K. Saxena and S. Dasgupta, Nanoscale finfet based sram cell design: Analysis of performance metric, process variation, underlapped finfet, and temperature effect, *IEEE Circuits and Systems Magazine* **11**(3) (2011) 38–50.

- 33. T. Cakici, K. Kim and K. Roy, Finfet based sram design for low standby power applications, in *Quality Electronic Design*, 2007. ISQED'07. 8th International Symposium on, IEEE2007, pp. 127–132.

- 34. A. L. Deepak, L. Dhulipalla, S. K. Chaitra and C. B. Shaik, Designing of finfet based 5-stage and 3-stage ring oscillator high frequency generation in 32nm, in Advances in Engineering, Science and Management (ICAESM), 2012 International Conference on, IEEE2012, pp. 222–227.

- 35. R. S. Kushwah and S. Akashe, Finfet based tunable analog circuit: Design and analysis at technology, *Chinese journal of engineering* **2013** (2013) 1–8.

- 36. M. Yasir, M. S. Ansari and V. K. Sharma, Performance evaluation of a finfet-based dual-output second generation current conveyor, in 2018 IEEE 18th International Conference on Nanotechnology (IEEE-NANO), IEEE2018, pp. 1–4.

- 37. M. Alioto, G. Palumbo and M. Pennisi, Understanding the effect of process variations on the delay of static and domino logic, *IEEE Transactions on Very Large Scale Integration (VLSI) Systems* **18**(5) (2010) 697–710.

- 38. T. Ohguro, K. Okano, T. Izumida, S. Inaba, N. Momo, K. Kokubun, H. Momose and Y. Toyoshima, Analysis of fin width and temperature dependence of flicker noise for bulk-finfet, in 2009 European Microwave Integrated Circuits Conference (EuMIC),

| June 24, 2019 | 12:33 | WSPC/INSTRUCTION FILE | "Yasir FinFET CCII Paper"

16 M. Yasir et al.

IEEE2009, pp. 61-64.

- 39. L. Safari and S. Minaei, A novel super transistor-based high-performance ccii and its applications, *Elektronika ir Elektrotechnika* **24**(2) (2018) 50–57.

- 40. A. Reda, M. F. Ibrahim and F. Farag, Input-output rail-to-rail cmos ccii for low voltage—low power applications, *Microelectronics Journal* 48 (2016) 60–75.

- 41. Y.-S. Hwang, Y.-T. Ku, J.-J. Chen and C.-C. Yu, Inverter-based low-voltage ccii-design and its filter application, *Radioengineering* **22**(4) (2013) 1026–1033.

- S. Sharma, K. Pal, S. S. Rajput, L. K. Mangotra and S. S. Jamuar, Low-voltage variable current gain ccii based all-pass/notch filter, *Indian Journal of Pure & Applied Physics* 47 (2009) 149–152.

- E. Arslan, S. Minaei and A. Morgul, On the realization of high performance current conveyors and their applications, *Journal of Circuits, Systems and Computers* 22(03) (2013) 1350015-1-1350015-23.

- 44. M. Yasir and M. S. Ansari, Performance investigation of fin-shaped field effect transistor based multi output differential voltage current conveyor and its application in balanced modulator, *Journal of Nanoelectronics and Optoelectronics* 14(5) (2019) 705–715.

- 45. G. Ferri and N. C. Guerrini, Noise determination in differential pair-based second generation current conveyors, *Analog integrated circuits and signal processing* **41**(1) (2004) 35–46.

- F. Khateb, T. Kulej and M. Kumngern, 0.3 v bulk-driven current conveyor, IEEE Access (2019).

- 47. J.-W. Horng, M.-H. Lee, H.-C. Cheng and C.-W. Chang, New ccii-based voltage-mode universal biquadratic filter, *International Journal of Electronics* 82(2) (1997) 151–156.

- 48. L. Safari, E. Yuce and S. Minaei, A new iccii based resistor-less current-mode first-order universal filter with electronic tuning capability, *Microelectronics Journal* **67** (2017) 101–110.

- Analog communication dsbsc modulators https://www.tutorialspoint.com/analog\_communication\_DSBSC\_modulators.html., Accessed: 2018-05-10.